基于CPLD和Embedded System的LED点阵显示系统的实

2 软件设计和编写

2.1 主控电路CPLD芯片设计与调试

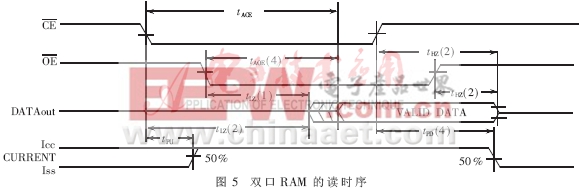

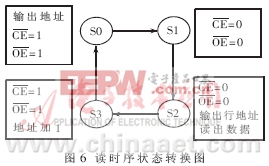

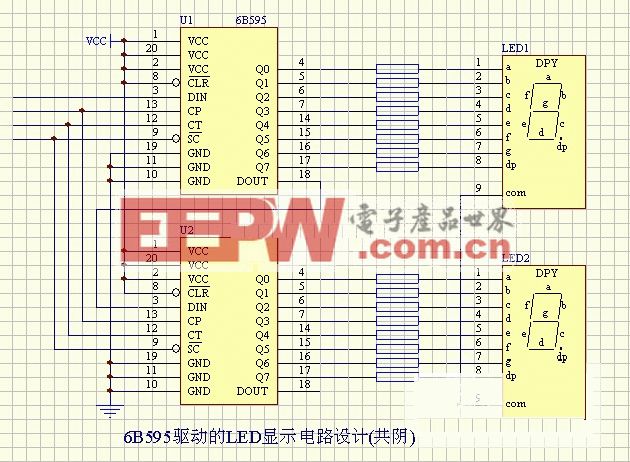

主控电路的功能是读取双口RAM中的数据并通过译码逻辑电路将数据显示在LED点阵显示屏的特定位置上。因为只用到单片机的一部分功能,所以使用CPLD芯片将MCU中的总线读控制器及其外围译码逻辑电路集成在一起。如若采用传统方案,就必须采用多片芯片;而使用CPLD后,只用一片芯片就可以实现所要的功能。总线读控制器是产生时序的电路,需根据存储器的读时序进行设计,只有保证正确的时序才能读出数据。双口RAM的读写时序和普通RAM的读写时序基本相同,如图5所示。在片选信号从高变低之前必须输出地址信号给双口RAM,然后再用读信号去控制

步骤S0 在RAM的片选CE使能之前输出地址;

步骤S1 选中RAM,输出读信号;

步骤S2 行计数器输出,读出RAM的数据并反相输出;

步骤S3 片选禁止,读禁止,地址计数器加1。

评论