基于FPGA的多通道HDLC收发电路设计

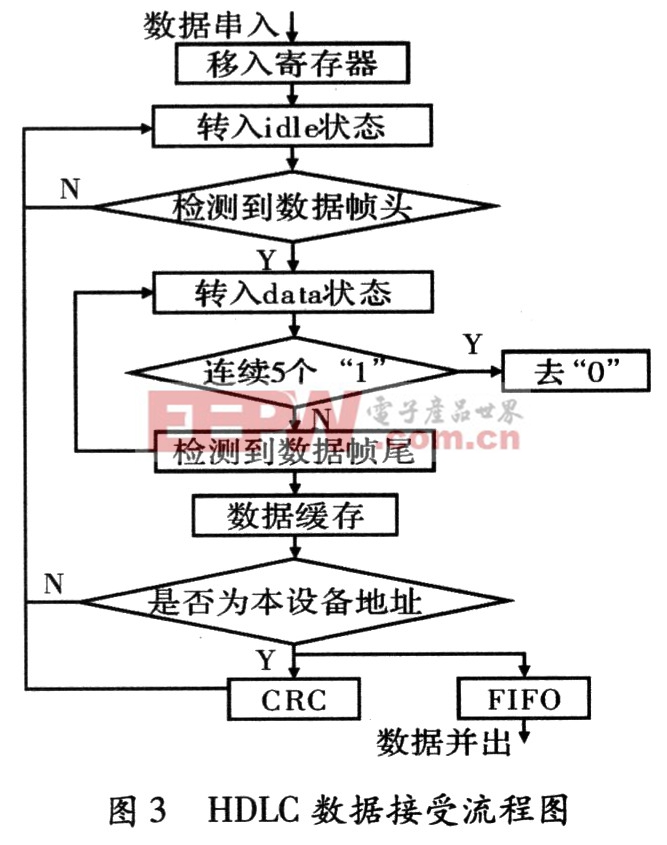

目的地址不是本设备的数据帧将被抛弃,流程图如图3所示。

3 实验结果和分析

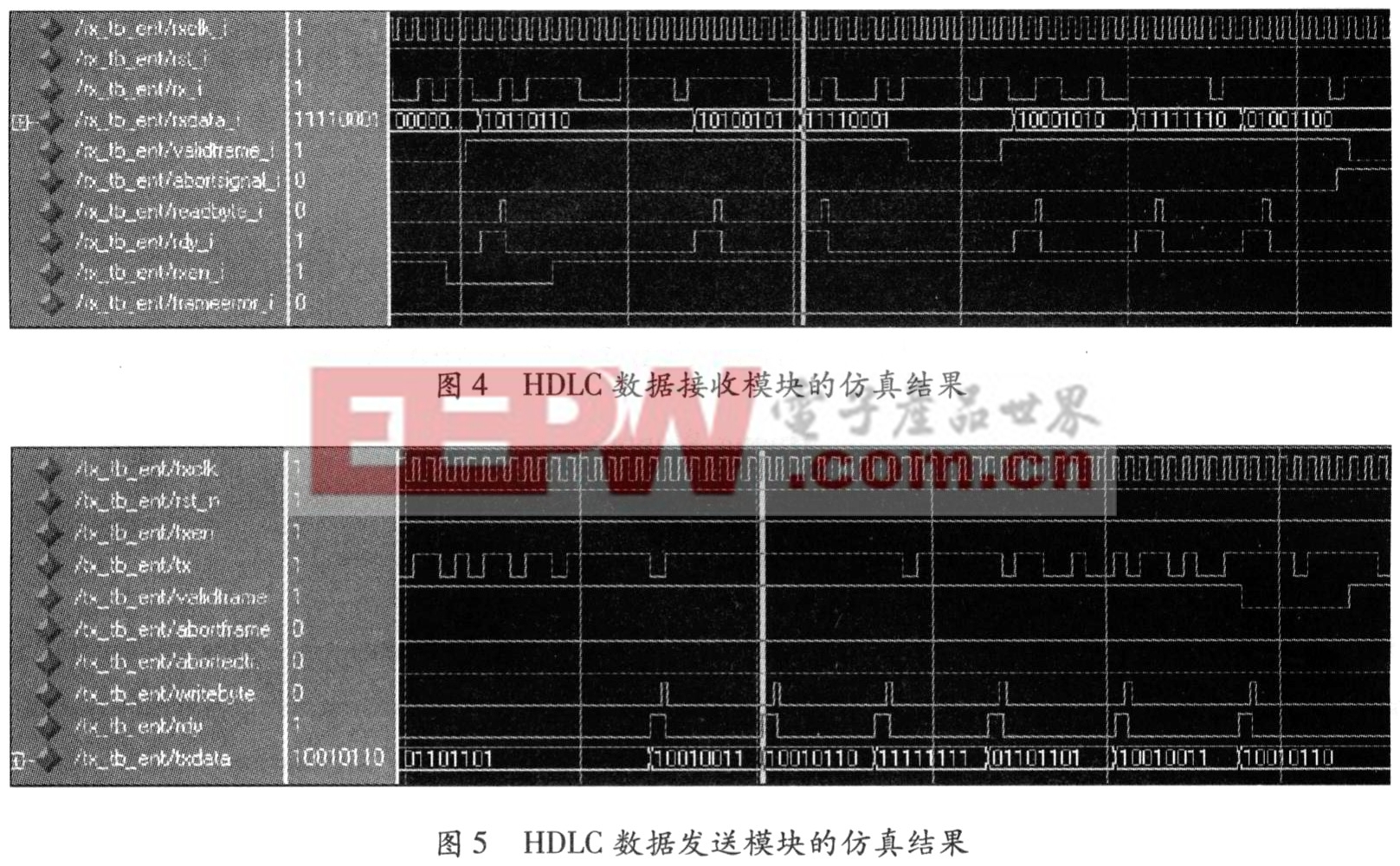

首先,在FPGA中实现一对HDLC数据收发电路,并在对收发电路进行仿真和相关测试。通过在Matlab开发环境下,生成相关的数据文件作为HDLC的数据源,在ModelSim SE 6.1的测试文件中直接调用,最后对比仿真结果和Matlab生成的数据源,可以得到满意的结果。仿真的测试代码覆盖率为100%,仿真结果和数据源完全吻合,可以认定电路的正确性及良好的可靠性。图4,图5分别为HDLC数据收发模块在ModelSim SE 6.1中的仿真图。

为合理利用FPGA内部的逻辑资源,对设计进行一系列布局布线约束:(1)由前期的论证可知,设计的矛盾主要集中在资源的消耗上,所有模块的优化目标定位为“Area”,除FIFO外,其他模块规划在一起;(2)将FIFO划分为独立的模块;(3)全局时钟绑定在Global资源上,并/串、串/并模块中的衍生时钟,根据和全局时钟的关系,设定为多周期路径。

实际数据收发的稳定性和可靠性,也跟单板、温度等有关系。仿真完成后,在单板上进行飞线,对特定的收发电路进行电气连接,进行回环测试法,即发送端输出的数据由其接收端接收回来进行测试。在常温下,经过30小时的长时间运行测试后,接收和发送的数据做了对比,没有发现丢数据包和错数据包的情况。由测试结果可知,该HDLC收发电路的具有稳定性和可靠性。高低温实验由于条件所限未进行,单板的温度特性可由器件的温度特性大概推知,这里不做讨论。

4 结束语

针对某遥控遥测平台的要求,文中提出了一种基于FPGA的多通道HDLC收发电路设计方案,并利用Altera公司的P2C70F672C8芯片来实现。目前,实现该电路的单板已经完成调试,并成功地应用于整机试验。实践表明,该电路实现简单、可靠性高、使用灵活等优点,具有一定的推广价值。

评论