基于FPGA的多通道HDLC收发电路设计

2 HDLC协议的FPGA实现

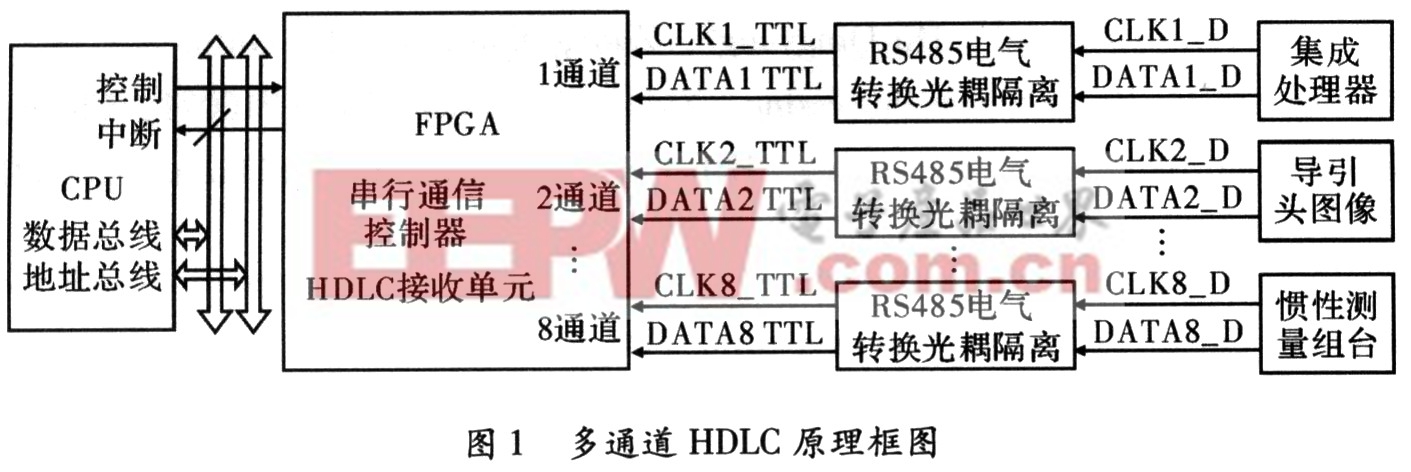

某遥控遥测平台为确保满足高速通讯、多通道收发、功能易于扩展配置的任务要求,中心控制器采用了以高性能的ARM7为CPU数据处理核心、采用FPGA设计串行通信控制器来收发多通道HDLC数据的一体化设计。本文引用地址:http://www.eepw.com.cn/article/191874.htm

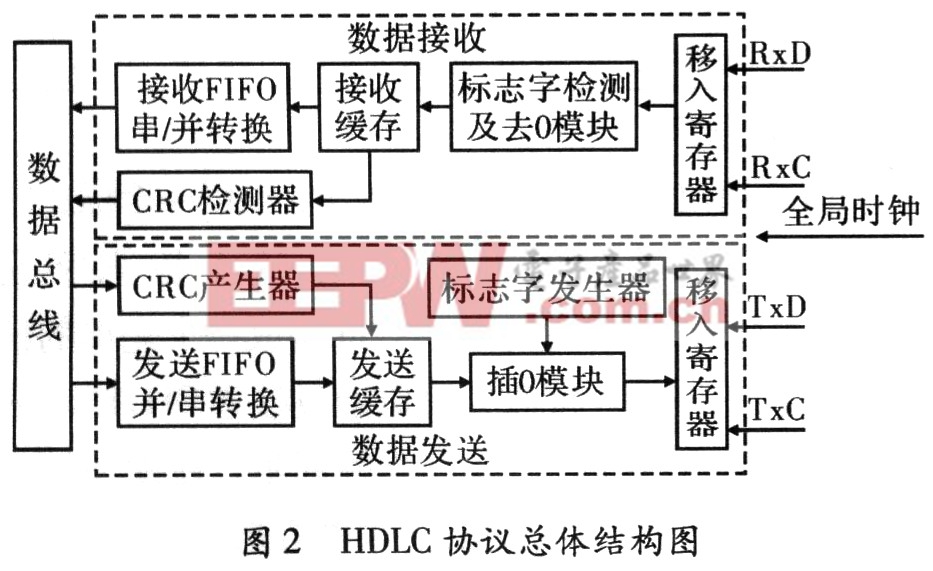

FPGA按照HDLC协议规程,接收并存储来自集成处理器等8个独立通道的数字量。系统先将外部输入的HDLC数据流由RS485电气特性转换为TTL电平,在此过程中用光耦进行隔离,以避免与外部设备之间的相互干扰,并且RS485芯片与光耦器件的相关电源使用由电气供给的独立5 V和5 V地。 HDLC协议总体结构框图,如图2所示,每个控制模块由时钟控制、编码/冲突检测、发送和接收FIFO等功能模块组成。在发送方向和接收方向,各有一个128 bit的FIFO,用于串行通道和CPU总线接口之间的数据缓冲。发送是接收的逆过程,这里以HDLC数据接收为例进行说明。

FPGA串行通信控制器接收HDLC数据的原理为:首先,将接收到的数据帧的消息字段和附加的状态字段移入,然后根据选定的寻址模式,对接收帧中的目的地址进行识别,确认数据帧的发送地址是否为本设备(站地址=77H),是本设备数据帧则进行接收数据并存储在FIFO中,当接收数据帧结束时,发出中断信号给ARM系统,请求接收HDLC数据。

评论