基于FPGA的2M误码测试仪设计

3.2 时钟电路

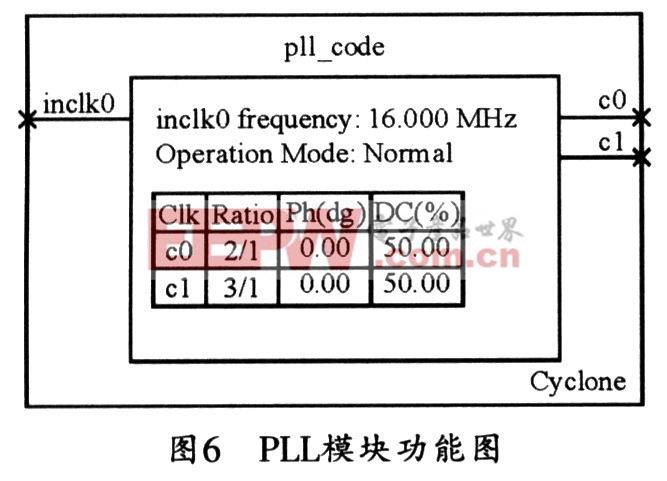

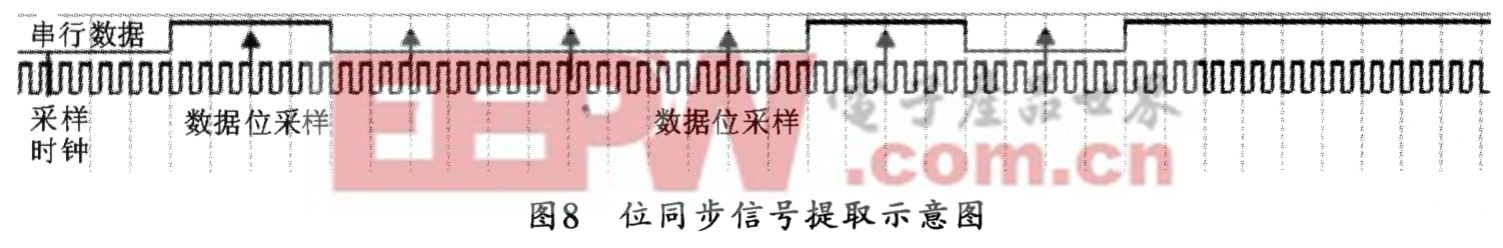

时钟是整个系统设计中重要的一环。序列发送、序列接收、对E2PROM模块的读与写、串口通信的波特率以及LCD显示等都离不开时钟信号的控制,这就需要系统内有一个基准的时钟模块来提供所需要的时钟信号。时钟模块可由锁相环和分频器模块构成。通过对QuartusⅡ中mega-function模块ALTPLL的定制可生成PLL,inclk0是外部有源晶振提供给FPGA的clk0引脚的16 MHz时钟,可经过PLL产生C0、C1两个时钟信号,其中C0是inclk0的2倍,为32 MHz,可作为序列接收模块中对测试码进行采样的采样时钟。而C1是inclk0的3倍,为48 MHz,设计时可将C1信号送入分频电路获得2 MHz时钟,作为序列发生器的时钟;也可将C1信号经分频电路获得1 MHz时钟,作为I2C控制模块的读/写及键盘模块的时钟信号;当C1信号送入UART控制模块和LCM控制模块后,可通过各自模块内部的分频电路获得所需要的时钟。图6所示的PLL模块中方框内表格中的各项内容分别表示信号名称、信号倍率、信号相位及占空比。本文引用地址:http://www.eepw.com.cn/article/191869.htm

3.3 测试序列发送模块的软件设计

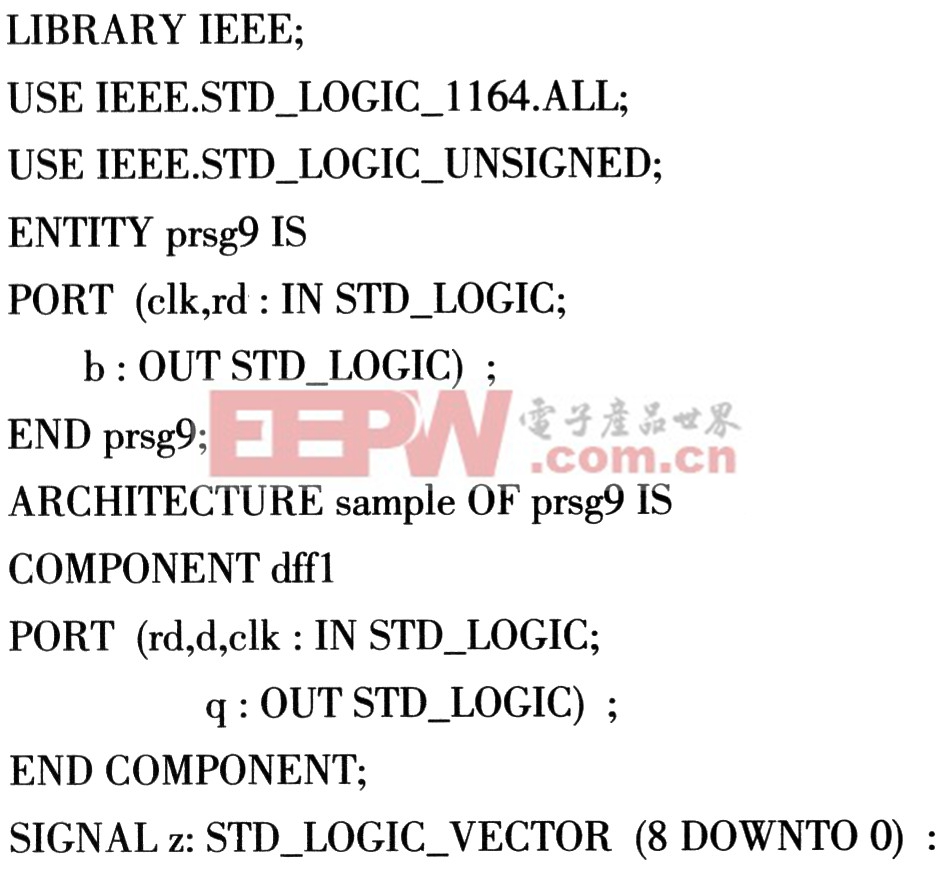

测试序列采用m序列时,ITU建议用于数据传输设备测量误码的m序列的周期是511,其特征多项式(本原多项式)建议采用f(x)=x9+x5+1,本文应用移位寄存器理论从本原多项式出发来产生m序列,本原多项式是f(x)=x9+x5+1的m序列的VHDL语言编程如下:

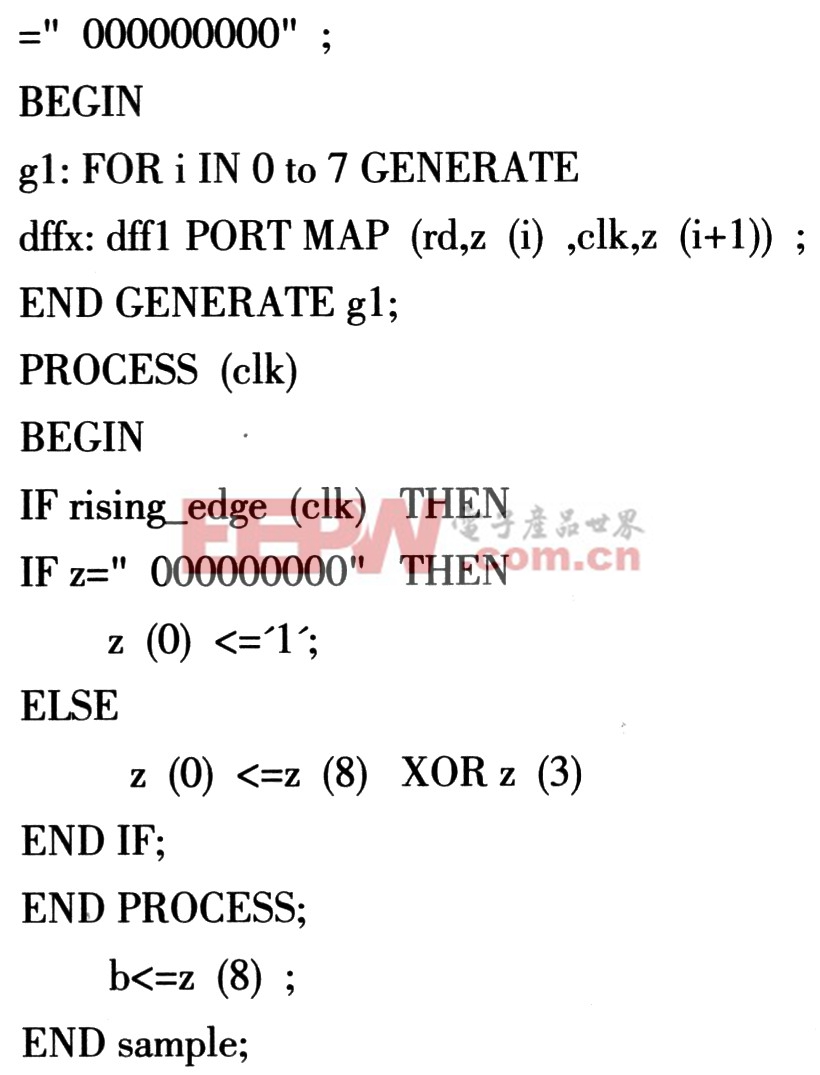

在Ahera的Quaaus II开发平台下,本原多项式f(x)=x9+x5+1的m序列的仿真波形如图7所示。

3.5 帧同步信号检测

对帧同步电路的一项基本要求就是要迅速发现失步,以便及时恢复同步。若在发送端插入帧同步码“0011011”,那么,在误码检测时,由于E1串行数据流中也会出现“0011011”这样的内容,因而难以判断哪些是帧同步码,哪些是数据内容,所以,在设计中,可采用计数器来进行帧同步码的定位。

评论