基于FPGA的2M误码测试仪设计

2.2 E1接口电路的设计

E1的标准传输线路码通常采用三阶高密度双极性码(HDB3,high density bipolar),它是一种双极性归零码,是广泛用于PCM线路的传输码型。本文中的E1接口选用非平衡的75 Ω物理接口(一收一发)。E1接口芯片ET2154是一路E1PCM-30/ISDN-PRI收发器,它集成有时钟数据恢复及发送E1脉冲成型的片内线路接口单元(LIU)和E1帧处理器(Framer),其各项指标符合ITU-T的G.703、G.704、G.706、G.823建议等要求。ET2154的线路接口功能主要包括三部分。第一是接收器,用于处理时钟和数据恢复;第二是发送器,用于形成波形和驱动E1线路;第三是抖动抑制器。本文引用地址:http://www.eepw.com.cn/article/191869.htm

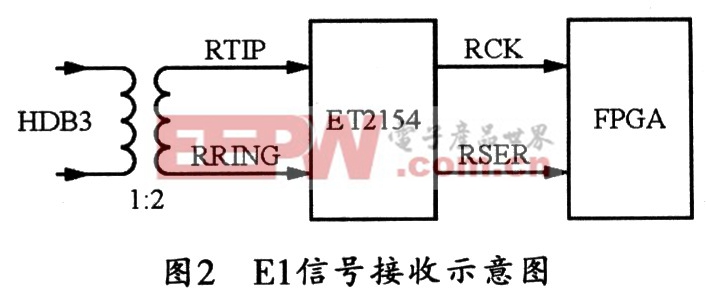

(1)E1线路接收接口

当HDB3码流从E1线缆经BNC接口进入,并通过一个1:2的变压器耦合至RTIP租RRNG输入管脚后,其接收模块将允许用户设置寄存器以匹配外部线路的阻抗。ET2154中的数据时钟恢复模块可从HDB3码流中恢复时钟和数据。从HDB3码流中恢复出时钟和数据可通过高倍采样来实现,首先由外部提供一个2.048 MHz的时钟信号,然后由芯片内部PLL将它16倍频到32.768 MHz 。即先对每位HDB3码进行16倍的采样,然后由时钟恢复系统利用16倍的采样时钟来恢复时钟和数据。其E1信号接收示意图如图2所示。

正常情况下(RTIP,RRING有信号输入),在RCK(接收方向恢复时钟)管脚输出恢复后的时钟信号。而当ET2154被配置成输出NRZ数据模式时,则在RSER管脚输出恢复出的串行数据信号并送入FPGA。

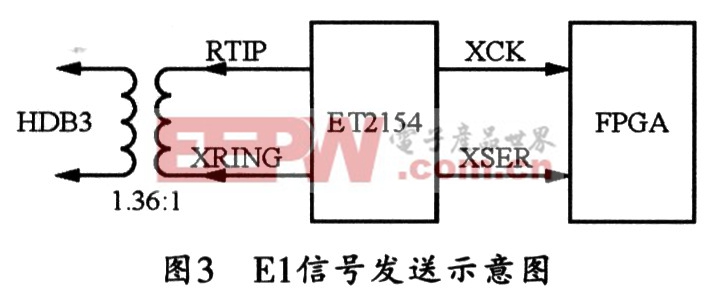

(2)E1线路发送接口

待传输的串行数据流一般由XSER (发送串行数据NRZ)管脚进入ET2154,并在XCK(发送方向输入时钟)管脚接收来自FPGA的2.048 MHz的时钟信号。ET2154主要由内部精密的数模转换器(DAC)来产生要发送到E1线路上的波形,这种波形符合ITU G.703规范。系统中的发送器可将模拟波形从TYIP、TRING管脚通过1:1.36的升压变压器耦合到E1线路上。其E1信号发送示意图如图3所示。

(3) E1线路控制接口

ET2154的工作方式和特性是通过对其外部管脚的控制来实现的。通常将这些控制管脚连接至FPGA的外部I/O口,由FPGA来进行控制。ET2154与FPGA的连接电路如图4所示。ET2154通过内部寄存器的配置来设置其工作方式,FPGA则利用8位数据/地址复用线AD0~AD7来对ET2154内部的寄存器进行设置,从而实现所需要的功能。

3 系统软件设计

在对系统软件进行设计时,可将误码测试系统的功能分为各个功能模块,然后用VHDL语言编程实现FPGA芯片内部各个功能模块的硬件逻辑,最后整合完成设计。本误码测试系统的FP-GA内核中的功能模块有时钟分配模块、序列发送模块、序列接收模块、LCM控制模块、I2C控制模块、RC232串口控制模块、键盘消抖及扫描处理模块、总控制模块等。FPGA内核中各个模块之间的相互关系如图5所示。

3.1 键盘处理模块

本系统中的键盘处理模块包括按键的消抖和键盘的扫描处理。由于键盘模块的设计直接和用户的输入控制相关,用户的一切控制结果都和按键输入相对应,所以可将总控制模块和按键处理模块放在一起考虑。

评论