基于阵列除法的数据接收/显示模块设计

表1以45 10/1010=101101 2/10102作为一个数值计算的例子,详细展示了图3所示的不恢复余数法算法流程图。首先将余数尺和被除数A联合左移一位,如果余数R的符号位S为0,将执行减法操作,否则应该加上除数D,如果余数大于零,则当前商位为‘1’,否则为‘0’,循环这个过程直到被除数A的所有位都完成运算。最后得商:0001002,余数:000101 2。本文引用地址:http://www.eepw.com.cn/article/191864.htm

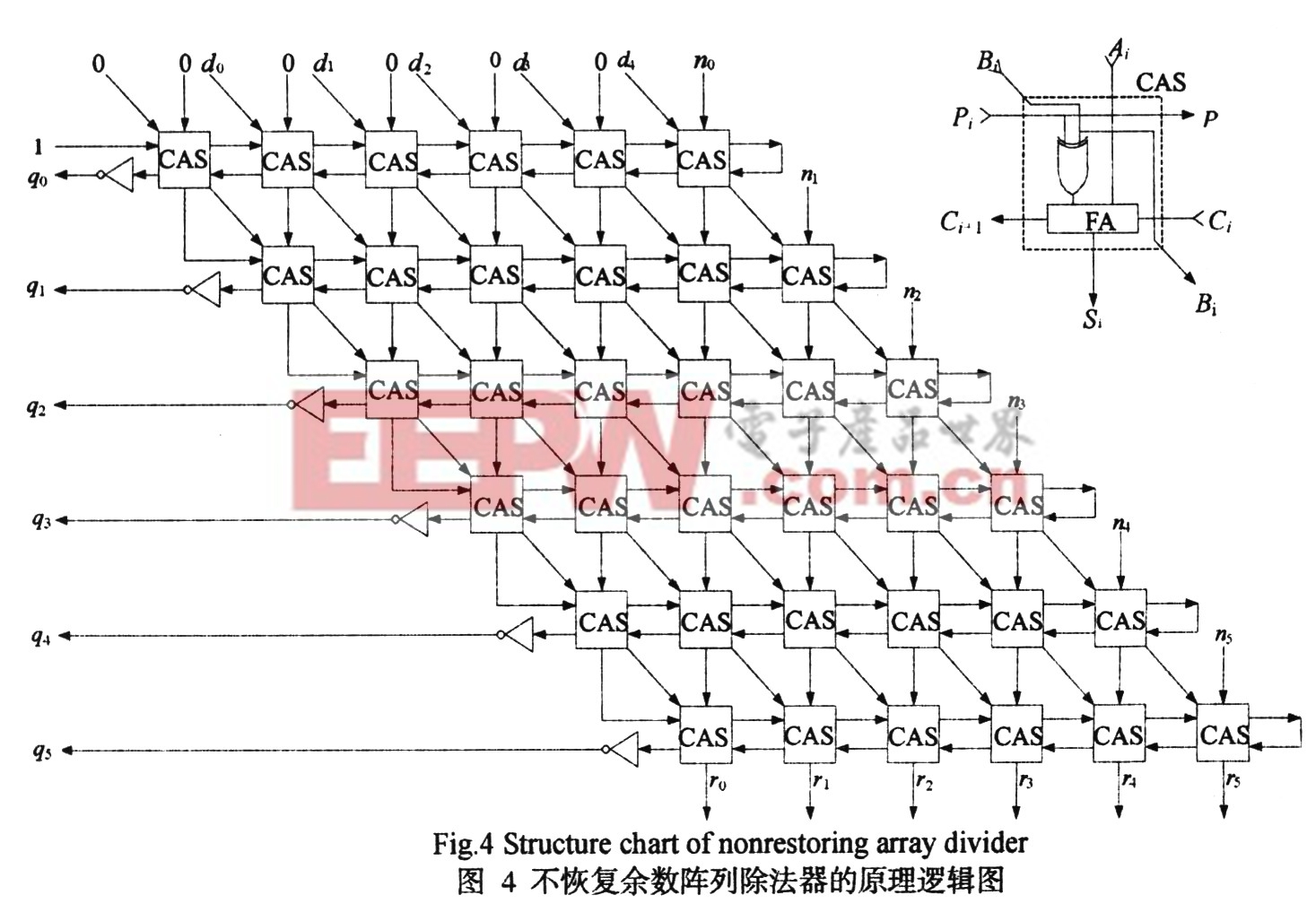

在除法中所需要的部分余数的左移可以用余数保持固定,而用除数沿对角线右移的等效操作来代替。如图4所示,不恢复余数阵列除法器可以用一个由可控加法/减法(CAS)单元所组成的叠接阵列来实现。不恢复阵列每一行所执行的操作究竟是加法还是减法,取决于前一行输出的符号与被除数的符号是否一致(最上面一行所执行的初始操作通常是减法,因此最上面一行的控制线P固定置成‘1’。当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产生一个商位‘0’,除数首先沿对角线右移,然后加到下一行的部分余数上。当部分余数不改变它的符号时,即产生商位‘1’,下一行的操作应该是减法。

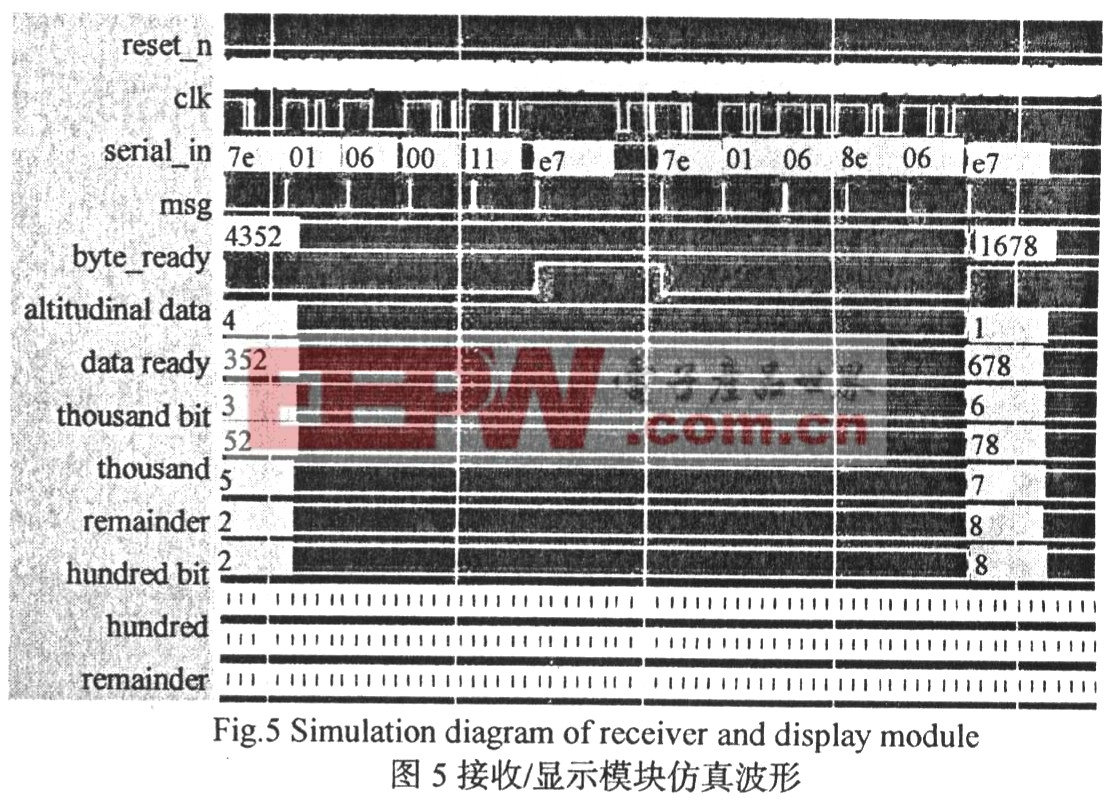

3 仿真验证

图5的仿真结果说明了数据接收/显示模块的功能特点。串行高度数据接收模块将串行数据转换为并行报文数据,从并行报文中提取出高度数据(1100h=4352,068eh=1678),不恢复余数叠接阵列除法器将多位二进制编码的高度数据转换为千、百、十、个位BCD码送到扫描七段码显示控制器。scanout信号选择四位七段共阳极数码管的某一位,leddata分别对应7个阴极引脚,对应分段字符串“abcdefg”,实现一位一位轮流点亮显示。由于视觉的记忆性,看到的是稳定的多位十进制高度数据显示。从仿真结果图中可见其与前述设计思想完全吻合。

4 结论

采用不恢复余数阵列除法设计的BIN码到BCD码转换器,仅需少量的移位、加/减法等操作,该算法逻辑简单,结构规整,速度高,非常适合实时性要求较高的场合,而且非常容易向其它进制转换扩展。以异步串行数据接收、阵列除法及动态显示等技术为基础的脉冲雷达高度表串行高度数据接收/显示模块作为一个工程的子模块,在某雷达高度表的设计中已经得到应用。

评论