基于CPLD的异步串行通讯控制器的研究与设计

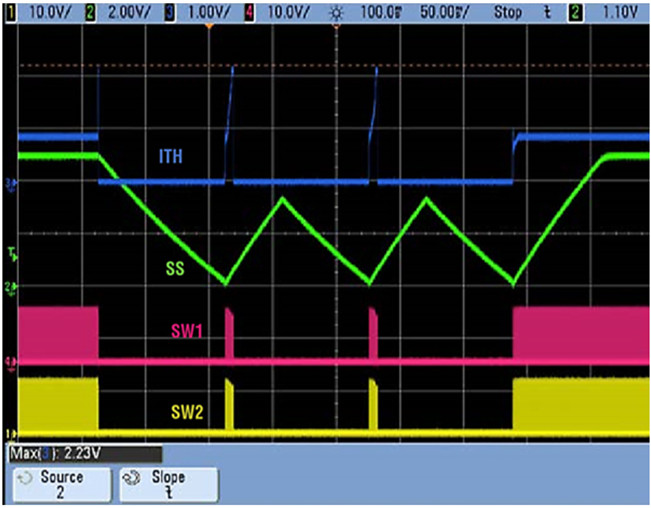

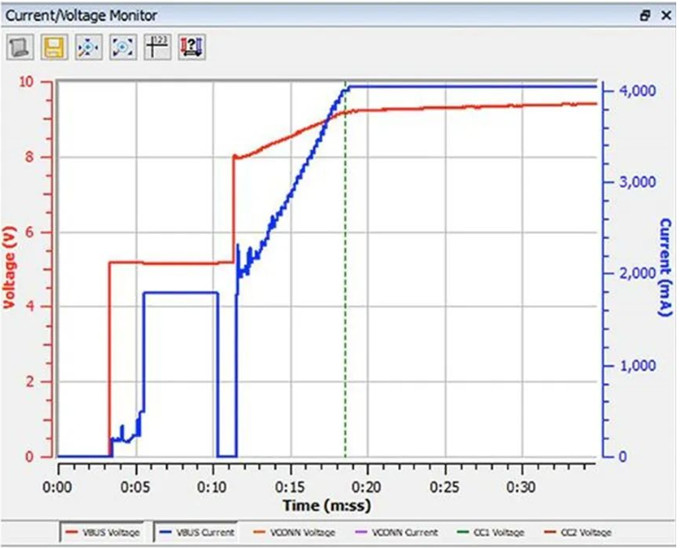

采用Xilinx公司的ISE工具发送和对接收这两个关键模块分别进行仿真,发送模块的时序波形图如图5所示,接收数据模块的时序波形图如图6所示。

在发送模块的仿真测试程序中,让CPU的数据总线连续发送55H,AAH,5AH,A5H,并在控制器的模式控制寄存器中设置发送的数据位5位,1个奇偶校验位(偶校验),1个停止位。在TxRDYn信号变低的时候,开始发送一帧新的数据。根据图5中数据输出信号Sout上信号变化的情况可以验证该模块设计是正确的。

在接收模块仿真波形图中,Sin信号是负责接收串行数据的信号线,RBR是该控制器内部的缓冲寄存器,负责存储经过串并转换后的数据,RxRDYn是控制器的外部信号,用来告诉CPU,控制器已经转换完一帧数据,CPU可以把数据从缓冲寄存器中取出。中断信号INTR会在数据传输完后,产生一个正脉冲。在测试接收数据模块的文件中,使产生一个连续的AAH和56H的串行数据,在图6中可以看到在Sin信号每接收完一个数据帧后,数据便存入RBR寄存器,RBR寄存器的数据位AAH和56H,并且在AAH传完后,RxRDYn立即变为低电平。

5 结语

本文在对异步串行通信协议进行分析的基础上,根据实际工程的需要,对异步串行通信控制器进行了详细设计,并结合CPLD器件,采用VHDL语言,对设计方案进行了实现和验证,通过最后时序仿真的波形图得出了设计方案的正确,而且加载了该设计程序的CPLD在实际工程中能够很好地与处理器进行连接来收发数据,从而为那些没有串行异步接口的处理器提供一个比较理想的设计方案。

评论