基于CPLD的异步串行通讯控制器的研究与设计

串行数据帧与接收时钟是异步的,所以接收器功能实现中的关键是接收器时钟与每个接收字符的同步。一个有效的方法是接收器采用高速率时钟对串行数据进行采样,通常采样频率是位时钟频率的整数倍,也就是选择比较高的波特率因子。理论上倍数越高接收数据各位的分辨率越高,实际中一般最大选择16倍。

接收器应该尽可能地在靠近每个数据位周期的中心处进行采样。如果接收器能很好地预测起始位的开始,那么它可在起始位的下降沿到来之后,等待半个位周期再采样数据位。此后,接收器每等待一个位周期采样一个数据位,直至收到最后一位为止。

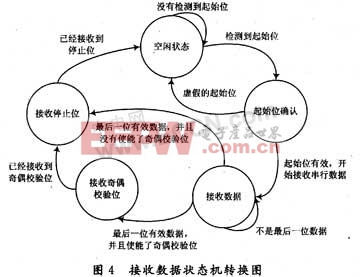

接收过程主要由一个3位状态机实现,其状态有空闲状态、接收起始位、接收数据位、接收奇偶校验位以及接收停止位。每一个状态表明了当前正在接收到数据属于哪一种字符,并且根据当前接收字符的状态驱动其他部件进行合适的操作。状态转换机的转换图如图4所示。

4基于CPLD的实现和仿真

可编程逻辑器件(PLD)是在20世纪80年代迅速发展起来的一种新型集成电路,随着大规模集成电路的进一步发展,出现了PAL和GAL逻辑器件,而复杂可编程逻辑器件CPLD是在此逻辑器件基础上发展起来的,它是由大量逻辑宏单元构成的。通过配置,可以将这些逻辑宏单元形成不同的硬件结构,从而构成不同的电子系统,完成不同的功能。正是CPLD的这种硬件重构的灵活性,使得设计者能够将用硬件描述语言(如VHDL或者Veritog HDL)描述的电路在CPLD中实现。这样一来,同一块CPLD能实现许多完全不同的电路结构和功能。同时也大大简化了系统的调试,从而能极大地缩短系统的研发周期。

于是我们在验证这一环节中,采用Xilinx公司的XC9500系列的XC95108 CPLD来验证该方案的合理性。在用VHDL语言实现图2的功能时,采用自顶向下的设计方法,先设计一个TOP顶层模块,它里面包括了接口控制电路模块,调制解调模块,发送模块和接收模块。其中接口控制电路模块包含了图2中的波特率控制逻辑电路,数据总线缓冲器和读写控制逻辑电路。设计实现中比较复杂的部分就是接口控制电路的实现。在接口控制电路模块中,设计了接收缓冲寄存器(RBR),发送保持寄存器(THR),中断使能寄存器(IER),中断标识寄存器(IIR),模式选择控制寄存器(LCR),调制解调控制寄存器(MCR),接收发送状态寄存器(LSR),调制解调状态寄存器(MSR),它们的存储器映射地址分别设置为000~110,因为该设计中把控制器设计为不能同时接收和发送,所以接收缓冲寄存器(RBR)和发送保持寄存器(THR)共用一个地址。其中,模式选择控制寄存器(LCR)用来设置,要发送数据的位数(从低到高发送),奇偶校验位的位数和停止位的位数。

评论