基于CPLD的异步串行通讯控制器的研究与设计

3异步串行通讯控制器的结构设计

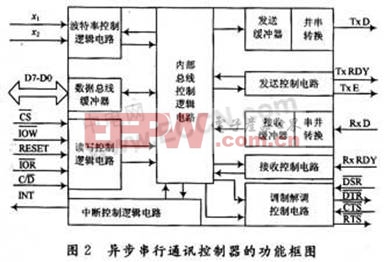

异步串行通讯控制器的内部结构可分为控制逻辑电路和寄存器组两大部分。在控制逻辑电路中,包括波特率控制电路、读写控制逻辑电路、发送控制电路、接收控制电路、调制解调器控制逻辑电路、中断控制逻辑电路和内部总线控制逻辑电路。寄存器组分为模式寄存器、控制寄存器和状态寄存器。结构框图如图2所示。

该异步串行通讯控制器提供的模式寄存器和控制寄存器,用来设定奇偶校验、传输速率、握手机制以及中断。在这个设计中,提供了3种奇偶校验选择:不采用、奇校验或偶校验。传输速率的设定是通过向模式寄存器中设置特定的数值,来选择波特率因子,再结合外部连入的时钟信号就可以得出传输的波特率了。它们之间的关系是:时钟频率=波特率因子×波特率。

3.1发送数据模块

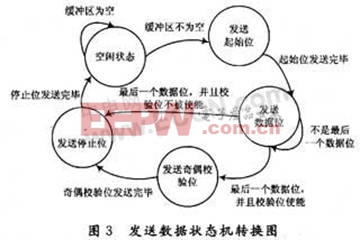

串行异步通信的发送器的实现要比接收器简单很多。没有数据要发送时,发送数据寄存器为空,发送器处于空闲状态;当检测到发送数据寄存器满信号后,发送器开始发送起始位,同时8个数据位被并行装入发送移位寄存器,停止位紧接着数据位指示数据帧结束。只有发送数据寄存器为空时,待发送的数据才能被装入,在设计中用一个TxE信号来告诉CPU此时控制器的发送寄存器为空。程序中使用计数器来保证发送数据时时钟的正确。这里使用一个状态机描述发送过程,图3是发送器状态机状态转换示意图。

评论