基于FPGA的TDI-CCD时序电路设计

2 TDI-CCD驱动时序

试验采用的是4 096×96 TDI可见光CCD。它的结构像一个长方形的面阵CCD,而实际上是线阵结构,其行数由4 096个像数(探测器)组成,列数由96个像素组成。积分级数为16.32,48,64,96可调,96级积分工作状态为PTDI16,PTDI32,PTDI48,PTDI64和PTDI1;

64级积分工作状态为PTDI16,PTDI32,PTDI48和PTDI1,PTDI64接-12 V电压;第48级积分工作状态为PTDI16,PTDI32同PTDIl,PTDI48,PTDI64接-12 V电压;第32级积分工作状态为PTDI16和PTDI1,PTDI32,PTDI48,PTDI64接-12 V电压;第16级积分工作状态为PTDI16,PTDI32,PTDI48,PTDI64接-12 V电压。

试验通过在硬件电路中使用八位开关加偏置电压实现积分级数的可调。这款CCD为八路输出结构,总频率为100 MHz,每组分别为12.5 MHz。其中第一路至第七路的有用信号为514个,其中有两个用于采集暗电平,第八路为518个其中有两个用于采集暗电平,时序设计中采用每路输出525个电平,多余的都为空信号用于采集噪声信号。

试验使用的这款TDI-CCD总共需要15路驱动信号,积分级数控制信号PTDI16,PTDI32,PTDI48,PTDI64在硬件电路中通过拨码开关加偏置电压实现,其他的11路行转移信号和水平移位读出信号在软件中实现(图2所示)。其中,PIG在级数选通时起撇出多余级数信号的作用;时钟PTDI1,PTDI2,PTDI3通过电平变换来控制信号电荷的行转移,频率为20 kHz;积分区信号经PTDI3转到PSG,再由PSG转到PTG,PTG转到水平移位寄存器控制信号PMl,PM2,PM3,PM4,最后由多路传输器输出。TDI-CCD电极逻辑关系如图2所示。

3 驱动时序的仿真实现

试验采用Altera公司的EP3C25Q240,使用这款FPGA中的PLL电路对20 MHz时钟倍频产生50 MHz时钟作为系统的主总时钟CLK。采用Altera

公司开发的QuartusⅡ作为开发平台,采用VHDL语言进行时序设计。系统有两路输入信号分别为总时钟CLK,复位信号Reset。15路输出信号作为TDI-CCD的输入时序信号(PTDI16,PTDI32,PTDI48,PTDI64和PTDI1),但是该时序不能直接驱动TDI-CCD,因为它的电压及功率值无法满足TDI-CCD的需要,所以在FP-GA与CCD之间增加脉冲驱动电路,试验采用CCD驱动器EL7155。

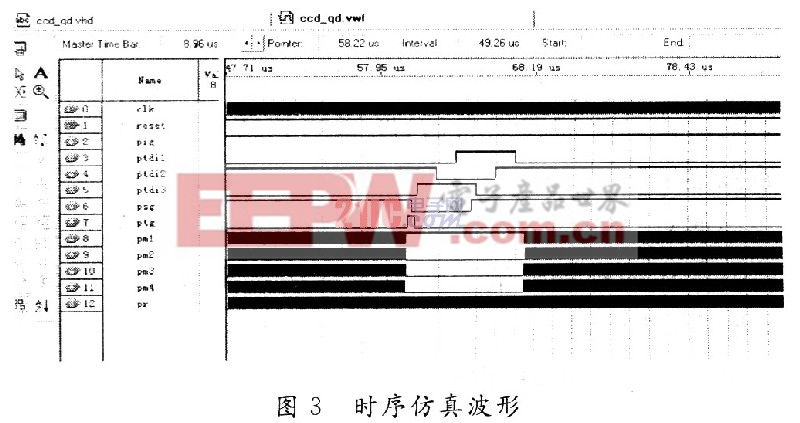

在QuartusⅡ中的仿真结果如图3~图5所示。由图3可看出TDI-CCD的工作过程可以分为两个阶段:行转移阶段和光积分阶段。在行转移阶段(如图4所示)通过时钟PTDI1~PTDI3的三相交叠脉冲的作用实现将积分电荷转移到水平移位寄存器中,PTDI1~PTDI3在每个时刻必须保证至少有一个高电平和一个低电平,而此时PM1~PM4保持不变,水平移位寄存器停止工作。

在光积分阶段(如图5所示),四相时钟PM1~PM4共同作用将水平移位寄存器中的电荷读出,每个阶段分别循环525次,此时三相时钟保持不变,同样的PM1~PM4在每个时刻也必须保证至少有一个高电平和一个低电平。四相时钟与三相时钟相比,比较适合较高的工作频率。

4 结语

该时序在硬件电路中成功驱动了这款TDI-CCD,验证了软硬件的正确性和准确性以及CCD的性能。同时该时序还有一定的灵活性,通过改变输入时钟的频率,它的输出频率是可以调整的,并且可以满足很高的频率要求。时序的稳定性比较好,在硬件电路中可以随时按复位按钮调整输出。在FPGA的基础上设计时序,使硬件电路设计简单化。

评论