FPGA的并行多通道激励信号产生模块

并行测试的实现途径分为软件方式和硬件方式。用软件方式实现并行测试,关键是对测试任务的分解和调度,但可能会产生竞争或者死锁现象。因此,在测试资源有限并且任务分解和调度算法不成熟的情况下,用软件实现并行测试会很困难。用硬件方式实现并行测试时,需要通过提供充足的测试资源来满足并行测试的需求,而并行测试过程中激励资源不足同样会造成任务分解和调度难度增加,甚至导致竞争和死锁,影响并行测试实现。因此,对多通道并行激励信号的需求也是影响并行测试的关键因素。

1 并行测试技术

并行测试技术是把并行技术引入测试领域中,可以较好地完成同时对多个被测对象(UUT)任务进行测试的一种先进的测试方法和技术,属于下一代测试技术范畴,是支撑NxTest ATS的新技术之一。它根植于并行处理技术,其宏观表现为:在并行测试程序的控制下对多个被测对象(UUTs)同时测试。相比传统顺序测试技术,它通过对系统资源的优化利用,可以大幅度提高测试效能及测试质量,提高测试资源利用率,降低整个武器装备测试成本。因此,研究并行测试技术对我国测试技术的发展和提高武器装备战时的快速维护保障能力具有重要意义。

2 多通道波形产生模块

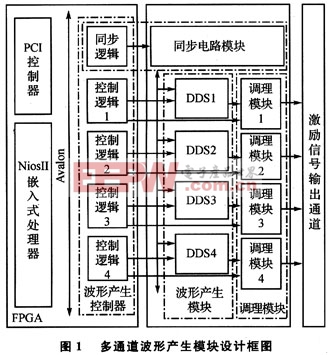

设计采用Altera公司的EP2C35作为整个系统的控制芯片,承担整个并行多通道信号产生模块的控制工作,内部主要包括Nios II嵌入式软核、波形产生控制器、PCI控制器等。

多通道波形产生模块主要包括4个子模块,分别为波形产生控制模块、信号产生模块、同步电路模块和调理输出模块。波形产生模块采用DDS技术,该技术产生的波形具备波形频谱纯净,稳定度高,切换时间短,频率、相位和幅度可调等特点。设计中采用ADI公司的AD9854芯片来实现此模块的功能。

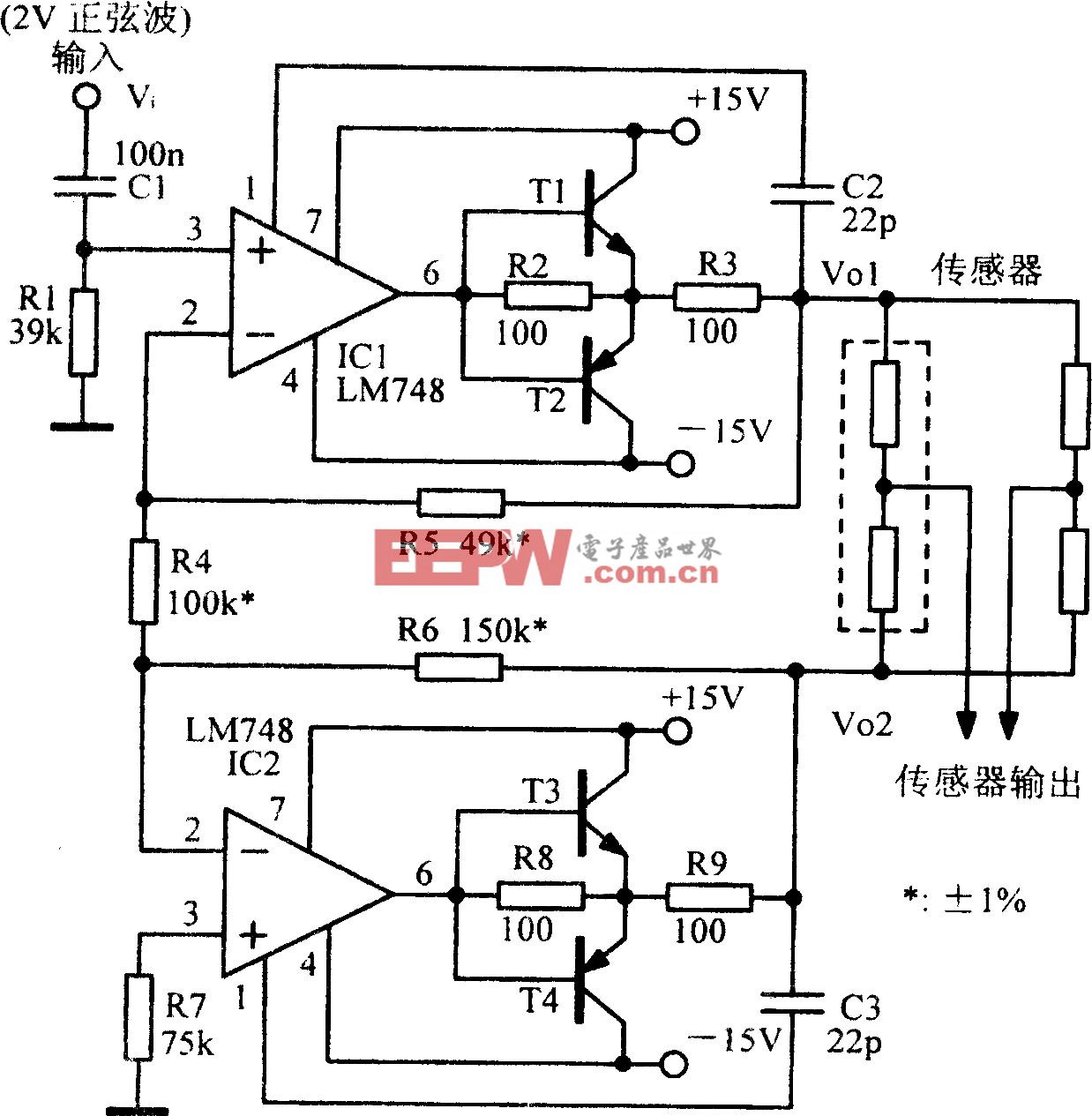

波形产生模块为4个通道,各通道之间相互独立,且可以在不影响其他通道工作的情况下独立地发起或者终止输出。同时为了满足测试系统对多路同步激励的需求,模块还需具备多通道同步的能力,并可以配置同步的通道数量及各通道间相互信号关系。输出激励的控制命令信号经PCI总线传输到FPGA中,FPGA将接收到的命令经过解析后分别送入同步模块、DDS信号产生模块和调理输出模块。各通道的DDS信号产生模块接收到控制命令后与同步模块配合产生同步或者异步激励,最后由调理输出模块实现输出波形的滤波和幅度控制。图1为多通道波形产生模块硬件设计原理框图。

评论