基于FPGA的动态可重构系统设计与实现

3.3.2 Virtex-4系列FPGA在该系统中的配置模式

Virtex-4器件的配置方法是用串行从模式、串行主模式、SelectMAP从模式、SelectMAP主模式、边界扫描模式(JTAG)之一将比特流载入内部配置存储器的:在该系统中采用可重构应用单元的FPGA配置模式有两种:

(1)JTAG方式(边界扫描方式)

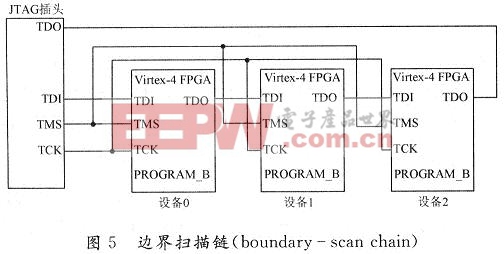

通过SPARTEN-3AN系列中FPGA提供的外部逻辑驱动JTAG专用引脚与同样4个JTAG引脚的两个应用FPGA及配置它们的PRROM串联起来,形成边界扫描链(Boundary-Scan Chain)将配置数据下载到FPGA中。在这种模式下,数据以每TCK一位的速度加载,如图5所示。

本文引用地址:http://www.eepw.com.cn/article/191610.htm

|

JTAG或边界扫描模式是一种行业标准的(IEEE1149.1或1532)串行编程模式。该模式通过电缆、微处理器或其他器件提供的外部逻辑驱动JTAG专用引脚TCK和JTAG测试时钟输入。当TCK保持在零状态时,测试逻辑状态应保持不变;TMS为测试模式选择,控制JTAG状态。出现在TMS的信号在TCK的上升沿由测试逻辑采样进入测试访问口(Test AccessPort,TAP)控制器;TDI:测试数据输入,测试数据在TCK的上升沿采样进入移位寄存器(SR);TD0:测试数据输出,测试结果在TCK的下降沿从移位寄存器(SR)移出,输出数据与输入到TDI的数据应不出现倒置。这种模式因其标准化程度和可通过同样4个JTAG引脚为FPGA编程的能力而广泛使用。JTAG方式常用于实现在线编程(In-System Programma-ble,ISP),对FPGA进行编程。

JTAG在线编程的特征也改变了传统生产流程,将以前先对芯片进行预编程再装到板上的工艺简化为先固定器件到电路板上,再用JTAG口进行编程。Xilinx的Virtex-4系列支持在一个边界扫描(JTAG)链中配置多个FPGA,每次,只配置链中的1个FPGA,大大降低了实现难度。

(2)PROM配置模式,是由SPARTEN3AN系列FPGA为每一个Virtex-4系列FPGA配置一组PROM控制线实现FPGA的下载。SPARTEN3AN系列FPGA和可重构应用单元的每一个virtex-4系列FPGA之间分别有一组PROM的控制线,每组都包括DIN(配置数据输入)、CCLK(配置时钟)、DONE(FP-GA配置完成)、PROG(触发重配置)、INT(配置初始化)5个信号,通过这些信号将配置数据下载到Virtex-4系列FPGA中去。两种方式互补,在边界扫描链发生断裂影响到整个链的功能时,可以使用PROM模式替补,提高了重构过程的可靠性。

4 结 语

基于SRAM的FPGA的问世标志着现代可重构技术的开端,并极大地推动了其发展。可编程FPGA可以根据不同算法设计合理的硬件结构,以达到提高执行效率的目的。动态可重构FPGA可以在程序运行中动态完成FPGA的不同配置电路功能,在不同时段执行不同的算法,实现了虚拟硬件可重构计算技术。这里提出的通过微处理器加FPGA结合串行菊花链实现可重构的方式,实现了动态可重构FPGA结构设计的一种应用。另外,该验证演示了系统中可重构控制器还可以结构模块化,能够工程化应用于其他设计中,具有灵活及可移植性强的优点。

评论