用FPGA解决65nm芯片设计难题

工艺尺寸缩小,连线的宽度和高度也随之减小,对功耗有不利的影响。减小铜连线的尺寸增强了电子散射和粒子边界效应。从而增大了连线阻抗,导致电路延迟和IR压降增大。在45nm以下,这些效应会更加明显。

工艺尺寸不断缩小的结果之一是导致待机功耗成为芯片总功耗中的重要因素。同时,芯片用户关心的问题从动态功耗转向待机功耗。由于待机功耗的增大,许多通信器件分开考虑总功耗预算和待机功耗预算,并逐步增加待机功耗预算的比例。由于这些器件大部分时间处于待机模式,因此,待机功耗成为最主要的问题。

与动态功耗不同,还没有简单的方法来降低待机功耗。芯片开发人员不得不使用复杂的工艺和电路设计方法,牺牲晶体管速率来提高Vt,并采取延长沟道长度等措施。

目前已经有技术突破来解决速率和待机功耗的问题。一种是应变硅,该技术将空穴和电子对的移动能力提高了50%,从而提升了器件速率。与其它技术进步不同,应变硅虽然提高了速率,但是并没有增加待机功耗。然而,它必须在芯片设计中采用新的布版规则,要求较严,导致了限制设计规则(RDR)这一概念的产生。RDR和可制造设计(DFM)在65nm以及更小工艺尺寸上越来越重要。

设计规则使开发过程越来越复杂

DFM重要性的增加以及RDR的出现导致芯片设计更加复杂。物理设计尤其需要更多的资源和简捷的物理设计自动工具。这些规则妨碍了版层重用,增加了新技术采用硬件IP模块的难度。结果导致在芯片设计上加大投入,需要更多的资源来处理新技术中的布版和设计问题。

除了越来越高的开发成本以外,芯片开发人员还面临其它的成本难题。65nm器件仅模板成本就高达2百万美元,而45nm器件模板成本会超过3百万美元。理想情况下,强大的财务支持是任何业务投入的基础,包括芯片开发计划等。然而,很多芯片开发项目缺乏足够的资金支持。

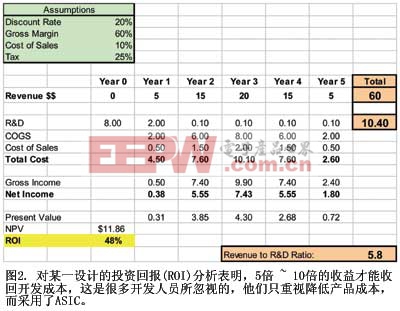

为了很好地进行财务分析,开发人员必须考虑时间、风险、收益和成本等一系列因素。尽管这看起来很难,但可以归结为经过认真设计的投资回报(ROI)分析(图2)。在很多情况下,分析表明,产品生命周期的总收益应是研发投入的5倍~10倍,这样才能收回开发成本。简单地看一下以收益百分比表示的研发开支(10%~20%),大部分成功的公司都会得出相同的结论。

评论