基于FPGA的数字脉冲压缩系统实现

采样数据首先存入FIFO中进行全局缓存,然后FFT单元从FIFO中读取采样数据,紧接着进行FFT运算,结果在流水输出时直接与匹配滤波器系数相乘,并将运算结果写入块RAMl中,最后IFFT单元从块RAMl中读取复乘后的数据进行IFFT(复用FFT运算IP核)运算,结果写入块RAMl后发送中断信号,等待DSP读取。

2.2.1 FFT处理单元的硬件复用

在系统中FFT处理单元通过使用软核Fast Fourier Transform v3.O来实现的。该IP核提供3种结构选择。

(1)管线级,数据流水I/0。这种结构将若干基-2蝶形单元级联起来,使得数据的输入、计算、输出可以流水进行,从而可以达到很高的处理速度,但资源消耗较大;

(2)基-2,最少资源消耗。这种结构采用单个基-2蝶形单元对输入数据进行变换,运算消耗的时间较长;

(3)基-4,突发I/O;这种结构采用单个基-4蝶形单元对输入数据进行变换,并利用块RAM来存储旋转因子,占用系统资源较少,在1个PRT内可以完成脉压结果的输出,从而在资源和速度这两者之间达到很好的平衡,也是设计中实际采用的结构。

FFT处理单元主要包括2个过程:数据I/O和运算过程,但两者不是流水执行的。FFT启动信号有效后,数据开始进行装载,装载完成后开始进行FFT运算;等待运算结束后,结果才可以输出。在运算过程中,不发生数据的装载或输出。

在数字设计中,FFT和IFFT处理单元时可以采用相同的结构来实现的。具体的方法是:在做IFFT运算前,先交换输入数据的实部和虚部,然后送入FFT处理单元按照FFT的结构进行运算,并交换FFT运算结果的实部和虚部,最后除以运算点数N,就可以得到IFFT的运算结果。

该IP核基于上面的方法同时具有进行IFFT运算的功能,通过实时配置端口FWD INV上的电平可以实现复用,分别完成FFT和IFFT运算。在FPGA设计中,利用结构复用减少逻辑单元块,不仅可以节约系统资源,而且能够减少结构间的硬连线及传输线时延,有利于提高系统的工作频率。

2.2.2 脉冲压缩模块的时序设计

由于FFT和IFFT的逻辑运算功能已经在IP核中实现,因此时序设计便显得尤为重要。在FFT(或IFFT)运算单元中,主要的状态与时序控制信号及其功能描述如表1所示。

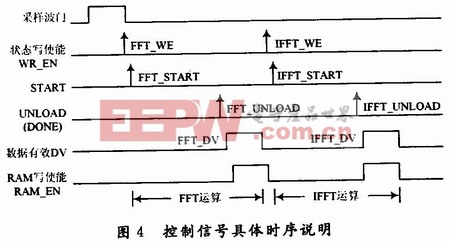

在采样距离门有效期间,将样本数据写入FIFO中进行缓存。采样结束后,通过FFT单元的写使能信号(NFFT_WE和FWD_INV_WE)将NFFT=010 10及FWD_INV_WE=1写入状态控制寄存器设定工作模式,接着启动START信号进行FFT运算,写使能信号与sTART之间仅差1个时钟周期。运算结束后,DONE信号有效1个时钟周期,输出使能信号UNLOAD与DONE同步,经过7个时钟周期后数据有效信号DV开始有效,FFT运算结果开始流水输出,同时与匹配滤波器的系数相乘,并存入RAM中。由于乘法运算的固有延迟,写使能RAM_EN延迟DV信号2个时钟周期。存储结束时,IFFT单元的写使能信号同时有效,并设定NFFT=01010及FWD_INV_WE=0,接着启动START信号进行IFFT运算。运算结束后,DONE信号(与UNLOAD同步)再次有效,IFFT运算输出结果在DV信号有效期间直接写入RAM中。单个PRT内各控制信号的具体时序说明如图4所示。

评论