基于FPGA 的低成本长距离高速传输系统的设计与实现

4.数据测试及系统性能分析

4.1 系统测试方案

测试方案主要对系统的静态功耗、动态功耗以及在50 米传输距离时的数据传输速率及相应的误码率进行测试。测试方案连接框图如图6所示。测试所用数据存在发送端例化的ROM 中,接收端FPGA 中例化有FIFO 和ROM,FIFO 用来存储接收的数据,ROM 中则存储有和发送端ROM 中相同的数据,用来计算误码率。同时,在接收端FPGA 中有接收数据计数器和错误比特计数器模块,通过设置SignalTap II 的触发信号和想观察的信号,就可以在SignalTap IILogic Analyzer 的窗口中实时的看到这些信号。

图6 系统测试方案

4.2 功耗测试

本系统通过直流稳压电源供电,方便计算整个系统的功耗。经测试发现,在不同的传输速率时系统的功耗差别不大,动态功耗典型值为数据传输速率100Mbps 时,系统消耗电流0.24A,供电电压3.3V,系统功耗为792mW。静态功耗测量时,不发送数据,但保持50 米双绞线接入,电流为0.20A,供电电压为3.3V,静态功耗为660mW。

4.3 误码率测试

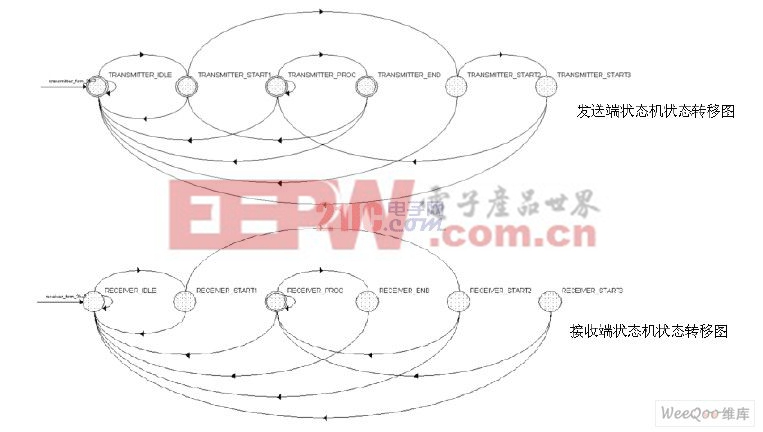

在发送端的FPGA 中采用ROM 来存储数据,通过状态机transmitter_fsm_3b 来控制数据的发送,状态转移图如图7上图所示。接收端则采用FIFO 来存储数据,同时接收端ROM 中存有和发送端相同的数据,以实现接受数据与原始数据的对比,计算误码率,接收端通过状态机receiver_fsm_3b 来控制数据的接收以及误码率的计算,状态转移图如图7下图所示。由于EP3C15F144C8 的RAM 大小总共只有512kbits,再加上signal tap 的开销,所以例化的ROM 和FIFO 比较小,ROM 大小为8Kbyte,内部存储数据由00H~FFH 一直重复,把一次ROM 数据的发送当成一个帧。每发送一次ROM 数据即比较一次FIFO 中与原始ROM 中的数据。重复发送20000 次,总bit 数等于20000 次*(8192*8)bit= 1469120000bit。因为接收端的数据时钟恢复和字对齐需要一定的时间,因而实际成功重复次数不到20000 次,可通过专门的计数器来确定实际重复次数。

图7 状态机状态转移图

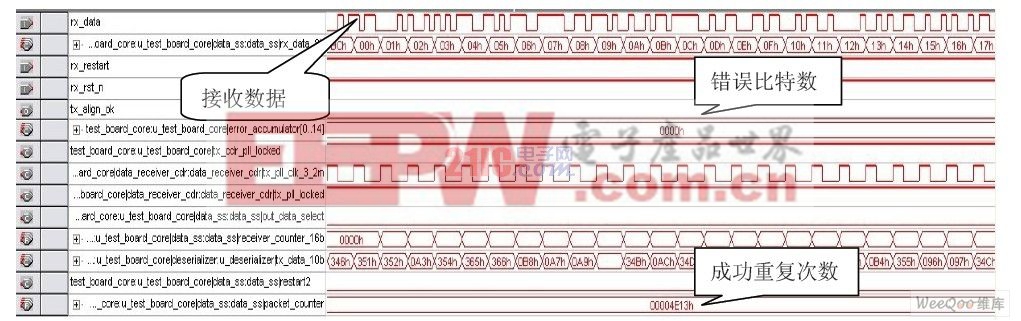

在接收端通过SignalTap II Logic Analyzer 实时查看接收数据rx_data、错误比特数error_accumulator 和成功重复次数packet_counter,图8 为SignalTap II Logic Analyzer 接收数据的窗口显示。误码率可通过式1 求得:

误码率=错误比特数/(成功重复次数×8192×8) (1)

图8 SignalTap II Logic Analyzer 数据接收窗口显示

传输速率及相应误码率如表1 所示,在传输数据为400Mbps,传输距离为50 米是误码率仍为0。由于选用的均衡器LM0074SQ 的极限速率为540Mbps,因而在数据速率为500Mbps 时误码率急剧增大。

表1 传输速率及相应误码率

5.总结

本系统高速数据远距离传输方案以Altera 公司的Cyclone III 系列EP3C5E144C8 为核心,使用LVDS 信号传输数据,通过信道编码、数据时钟恢复、预加重和均衡等技术的使用,保证了数据传输的稳定性和同步性,在传输速率为400Mbps,传输距离为50 米时,误码率为0。可以广泛的应用于各种高速远距离数据传输的场合。

Altera 公司新推出的Cyclone IV GX FPGA 中含有8 个收发器,具有时钟数据恢复(CDR)功能,并有在片内集成可编程预加重设置和可调差分输出电压(VOD)提高了信号完整性。本文的后续工作将在Cyclone IV GX 上实现本系统的所有功能,以进一步提高数据传输速率、传输距离、误码率等指标。

评论