应对FPGA/SDI子系统中的高速板布局挑战

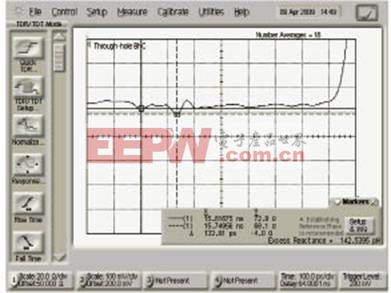

图2 SDI端口和SMPTE限制值的输入回波损耗图

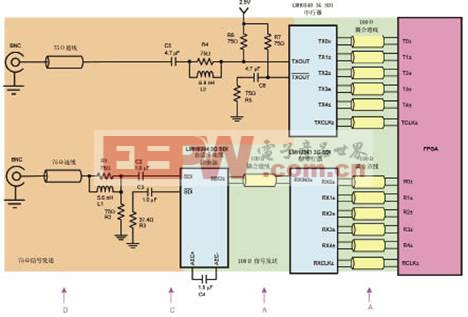

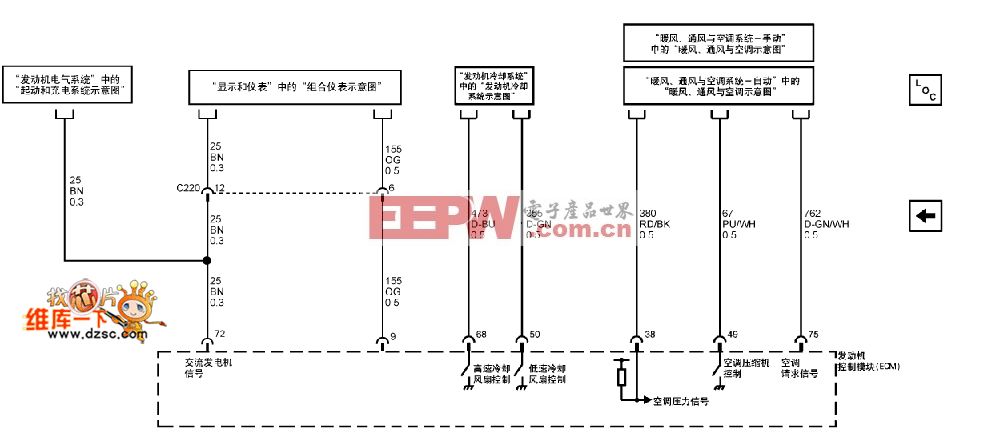

图3 典型SDI电路(仅显示高速信号路径)

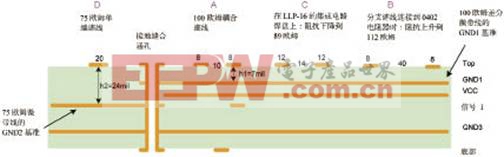

图4 具有75和100迹线单独接地参考的板堆叠

BNC连接器的布局

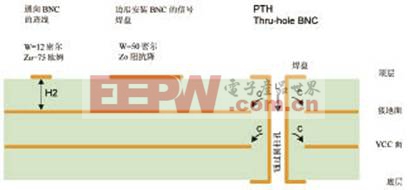

很多SDI板的常见问题是使用非优化BNC连接器布局,因此产生严重的阻抗失配、无法满足回波损耗要求,并削弱了设备的信号保真度。图5显示板的横截面,其中12密尔宽的微带线连接到50密尔宽的边沿安装BNC焊盘上。接地面被置于顶部迹线下的绝缘距离点上,以实现目标迹线阻抗。连接器的接合焊盘是宽微带线,因此焊盘的特征阻抗略低于迹线阻抗。焊盘具有较大的阻抗降,从而影响回波损耗和限制迹线的传输带宽。

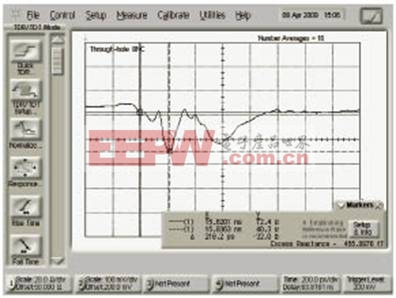

图5还显示了通孔BNC布局的横截面。内接地和供电面与镀通孔绝缘,以避免短路。圆柱孔带有一定的电感。每个接地或供电面的镀通孔都具有寄生电容。小间隔的大镀通孔将抑制容易造成大组抗降的多余电容。图6显示具有60密尔孔和20密尔间隔的设计不佳通孔BNC的阻抗形态,图中显示了镀通孔的阻抗从75迹线下降到40。

图5 BNC布局的横截面图

图6 设计不佳的通孔BNC的阻抗形态

设计良好的BNC布局

设计良好的BNC布局的目标是避免BNC布局与连接到布局的迹线间产生过多的阻抗失配,可以遵循信号路径查找板结构变化可能导致的阻抗失配。时域反射计是能够确定阻抗失配发生位置的仪器。可以使用电磁仿真器检查板布局设计中的阻抗变化。如果阻抗过低,应设计能够抵消过多电容的板结构;如果阻抗过高,应增加额外寄生电容使阻抗值接近目标值。通过正确的电感和电容值,可以建立具有所需特征阻抗的通孔BNC布局。图7显示良好的通孔BNC布局示例,图8显示非常接近75目标值布局的阻抗。

图7 良好通孔BNC布局的顶视图

图8 良好通孔BNC布局的阻抗形态

FPGA/SDI板的布局指导原则

FPGA/SDI板的数据传输率低于3Gb/s,信号转换时间约为100微微秒。SDI板布局的难点不在于速度,而在于计划一种布局策略以最大限度减少与75SDI端口很多外部元件的阻抗失配,设计大BNC控制器的受控阻抗布局和实施支持75和100迹线的板堆叠。可以通过遵循以下这些简单的布局指导原则解决这些难点:

评论