基于FPGA的多级小波逆变换实时系统设计

2 CDF9/7小波逆变换的VLSI实现

2.1 整体方案分析

离散小波逆变换模块处于JPEG2000解码系统最后一级,它负责将前端EBCOT解码得到的数据进行小波逆变换处理以获得重构图像信息。由于逆变换模块的数据并不如正变换模块一样直接来自外部数据总线,而是来自前端的EBCOT解码数据,因此既不能用协议的方式规定输入数据的顺序,也不能保证EBCOT解码数据等时间间隔均匀输出,所以在前端EBCOT模块和离散小波反变换模块之间需要使用存储器进行缓存。

由于连续小波基能够消除图像的方块效应,因此为了降低高倍压缩时各编码块之间的边际效应,在满足工程实现要求的同时提高压缩质量,一般需要选择尽可能大的图像块进行处理。显然,这受限于原始图像本身的大小和存储器的大小。为避免小波变换的图像尺寸受存储器的大小限制,同时避免使用昂贵的大内存FPGA芯片,本设计中选择使用片外存储器缓存接收到的数据帧。

2.2 整体方案设计

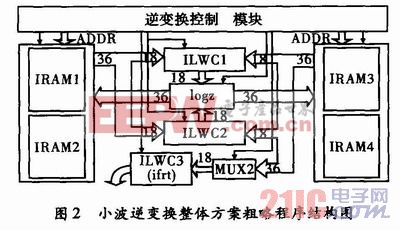

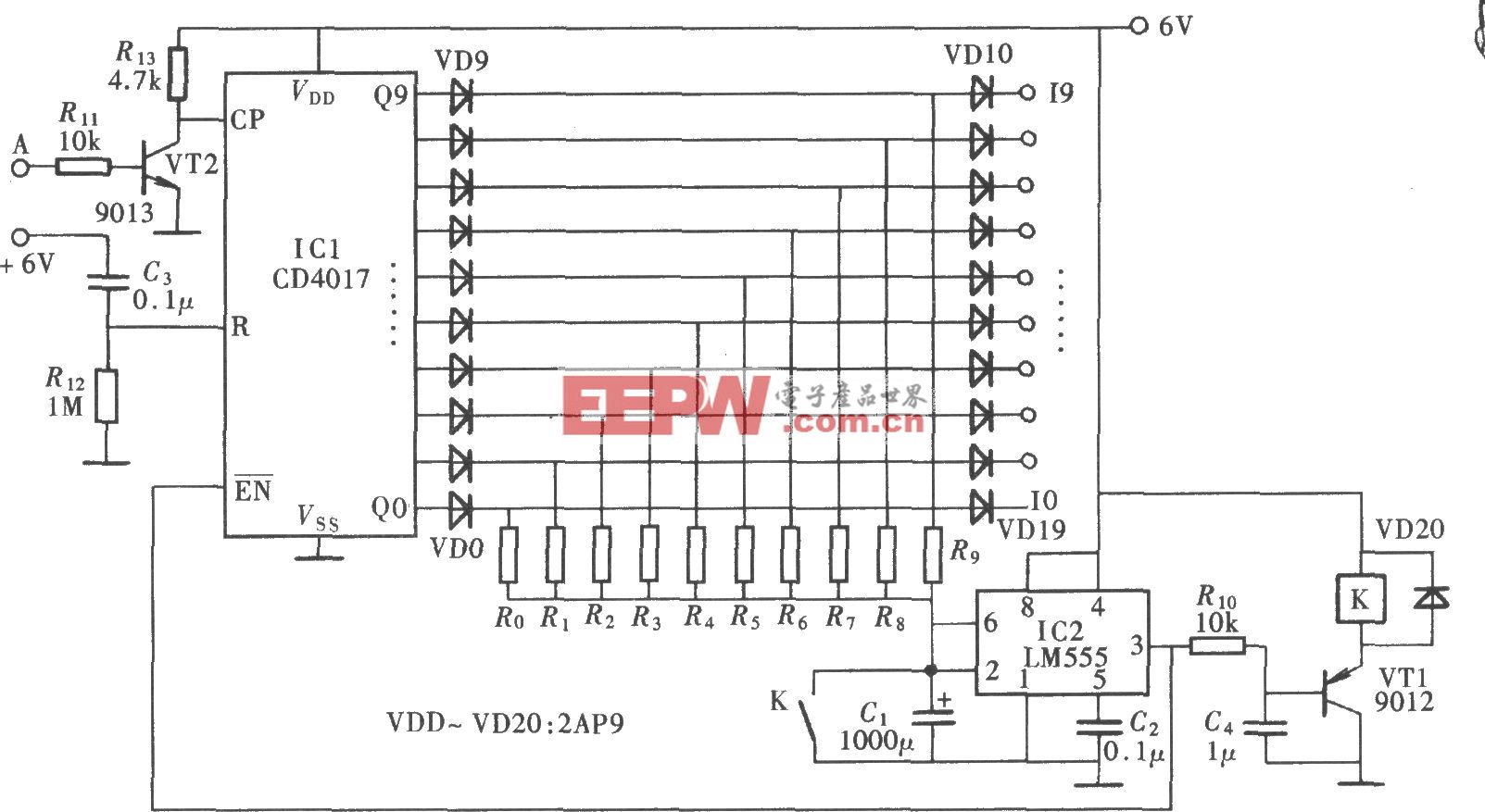

小波逆变换需要在接收到完整的一帧数据之后才能启动,而且对于N个像素点的图像,完成JPEG2000解码系统中的3层小波逆变换处理,需要M=N/16+N/16+N/4+N/4+N+N=2.625N个时钟周期。为了降低系统功耗,本设计并不采用倍频实现,而提出了一种双路并行的实现结构,其整体方案粗略结构如图2所示。本文引用地址:http://www.eepw.com.cn/article/191347.htm

图2中箭头指示数据流向,箭头中的数字表示数据宽度,2对片外存储器采用乒乓方式轮询切换。本方案首先使用两路并行的核心计算单元(ILWC1和ILWC2)完成前3列2行逆变换处理(第3层小波逆变换、第2层小波逆变换和第1层小波列逆变换),这期间的数据交替的在IRAM1和IR-AM3或者IRAM2和IRAM4之间存取;然后再使用第3个独立的核心计算单元(ILWC3)完成剩余的最后一次小波逆变换处理(第一层小波行逆变换),处理完毕的数据。由于单个小波系数位宽为18 bit(4 bit小数位确保精度要求),因此片外存储器每个36 bit的存储单元中可以同时存放两个小波系数。在前3列2行逆变换处理过程中,每次读取的2个小波系数可以分别提供给ILWC1和ILWC2并行处理,在第一层小波行逆变换时则由一个二通道选择器(MUX2)对数据的高、低18 bit位进行选择分时提供给ILWC3。数据组织模块(Iogz)的功能就是将ILWC1和ILWC2这两个处理模块完成的行、列变换数据进行合并重组,以便对片外RAM进行读写的36 bit外部总线数据总是由两个18bit小波系数分别以总线数据的高18bit和低18 bit的形式组合而成。

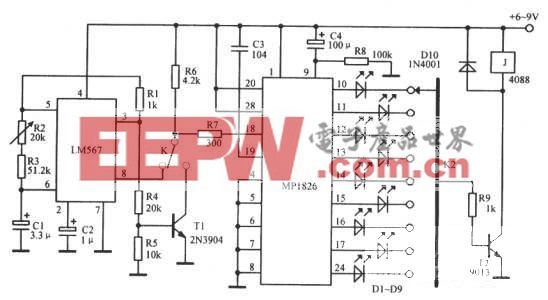

基于以上实现方案,对于N个像素点的图像,首先由ILWC1和ILWC2完成3列2行逆变换需要M1=N/32+N/32+N/8+N/8+N/2=0.812 5N个时钟周期,然后由ILWC3独立最后一层行变换需要M2=N个时钟周期。因此,两个处理过程所需的总时间M=M1+M2=1.812 5N不超出允许的存储器占用上限(2N),能够保证对连续输入的小波系数进行实时的处理。4个存储器轮询状态和FPGA的功能状态参见图3。

评论