基于FPGA+DSP的雷达高速数据采集系统的实现

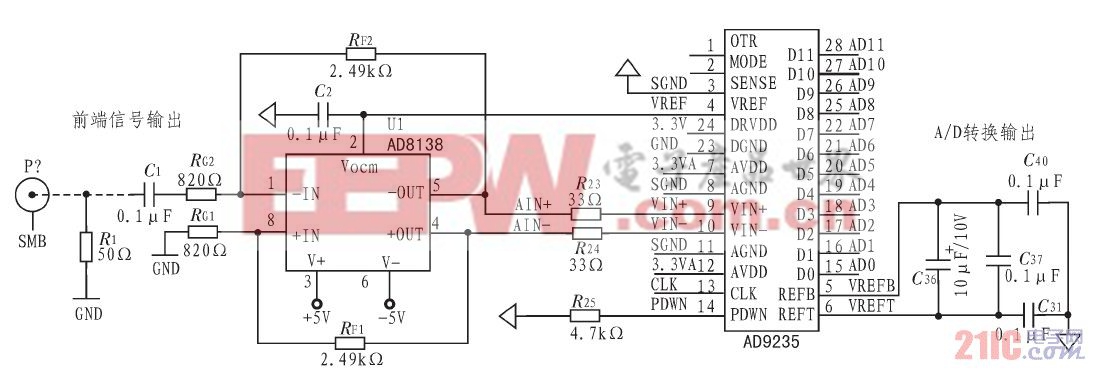

2 A/D转换电路

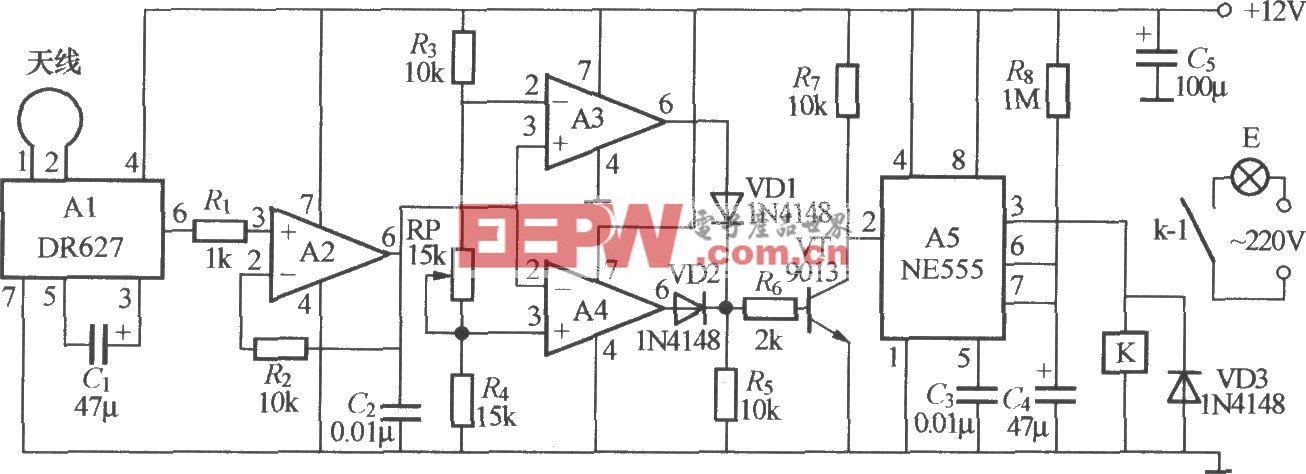

A/D转换电路是整个系统的重要组成部分。对前端输出约-25~25 mV,带宽为20 MHz的射频信号数字化,设计采用模数转换器芯片AD9235,最大采样率40 Mb/s,12 bit数据输出,信噪比RSN=70 dB。AD9235是差分输入,单端信号输入需要A/D驱动芯片,选用低失真差分A/D驱动芯片AD8138,图2为A/D转换电路,AD9235模拟输入设置在2VPP,参考电压VREF采用内部1 V参考电压,同时还作为驱动芯片AD8138的共模电压。利用AD8138对输入信号进行放大,放大倍数RF/RG=2.49 kΩ/820 Ω≈3。因此,经过AD8138单端差分转换及放大输入信号范围为25~175 mV。

图2 A/D转换电路

3 FPGA接口设计

3.1 时钟设计

采用30 MHz外部晶振作为整个系统的时钟源,利用XCV250内部的时钟管理器DCM,分别为AD9235、异步FIFO、TMS320C6201提供时钟源。 DCM输出CLK0的30 MHz时钟作为AD9235采样时钟和异步FIFO的写周期WR_CLK。

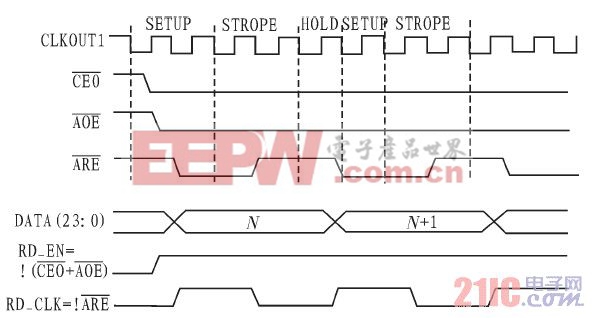

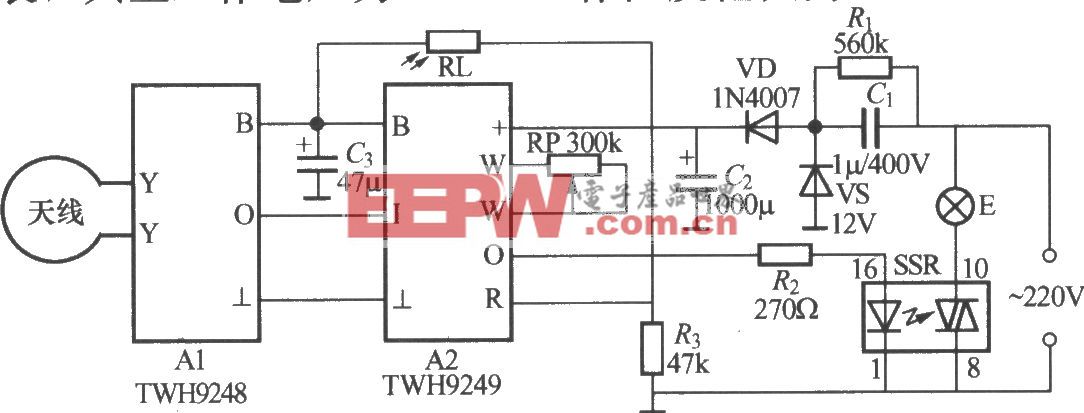

利用DCM数字频率合成器输出CLKFX作为TMS320C6201的时钟源。公式:DCM输出CLKFX的频率=输入时钟CLKIN的频率×(M/D),取M/D=5/3。这样DCM为TMS320C6201提供50 MHz时钟,经过4倍频,DSP系统时钟为200 MHz,外部存储EMIF时钟CLKOUT1为200 MHz。设置CE0空间控制寄存器的参数,使FIFO读时序SETUP、HOLD等于一个CLKOUT1周期,STROPE等于两个CLKOUT1周期,读时序如图3所示,读第一个数时,EMIF会自动维护最小2个时钟周期的建立时间,后续数据读取,建立时间为1个时钟周期。FIFO读时钟周期约为50 MHz,比A/D向FIFO写数据时间快,保证系统实时采集。

图3 读FIFO数据时序

评论