基于FPGA的高性能DAC芯片测试与研究

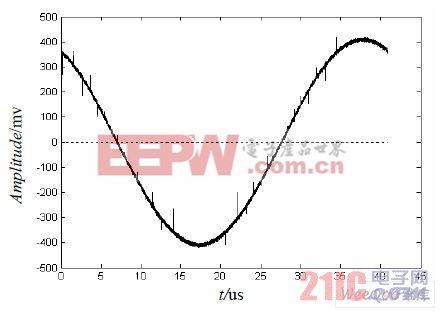

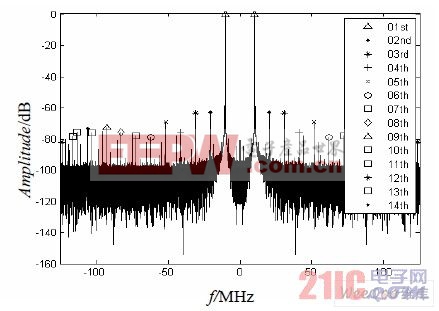

Sin 信号测试:输入正弦波频率25 kHz,AD 采样率为100 MHz/s,输出数字信号经过Matlab 分析计算后,测得SNR是58 dB,SINAD 是57.75 dB,SFDR 是62.84 dB,THD 是58.62 dB,ENOB 是9.3 位。时域波形和FFT 变换后14 阶谐波的频谱如图4 和图5 所示。

图4 sin 信号输出时域波形

图5 sin 信号输出频域波形

4 结语

以12 位、250 Ms/s DAC 芯片为例,在FPGA 的基础上使用回路测试法,测试了其静态特性参数和动态特性参数。实验结果表明,可以有效地测试DAC 芯片的静态特性参数和动态特性参数。同时可以测试不同分辨率和采样速度的DAC 芯片,测试结果比普通模拟测试仪器的精度高,测试系统比专用DAC 自动测试设备成本低。

评论