基于FPGA的部分响应CPM信号解调器的设计

在现有的民用、军用通信系统的众多应用领域中,为了实现高速率数据传输,提高频谱利用率,必须采用带宽效率更高的编码、调制技术。在众多的调制方式中,连续相位调制信号(CPM 信号)具有恒包络特性,它用于承载信息的相位轨迹连续变化,因此该类信号拥有较高的带宽效率。基于CPM信号的恒包络、带宽紧凑和能量利用率高等优点,近几年来,它受到广泛的研究与应用。

本文引用地址:http://www.eepw.com.cn/article/191289.htm文中分析了二进制,部分响应L=2 的连续相位调制方式,提出了一种该调制方式下解调器的FPGA 设计方法,并运用VHDL 硬件描述语言实现。

1 CPM 的基本原理

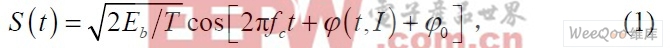

连续相位调制信号可以用式(1)表示:

式(1)中, b E 表示信号的码元能量,T 是码元间隔, 即表示信号幅度。c f 是载波频率,φ (t, I )是带有传输信息的信号相位函数,其中I 表示发生的符号序列。φ (t, I )的表达式如下:

即表示信号幅度。c f 是载波频率,φ (t, I )是带有传输信息的信号相位函数,其中I 表示发生的符号序列。φ (t, I )的表达式如下:

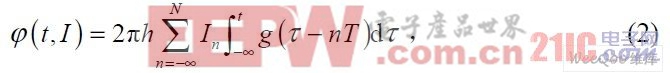

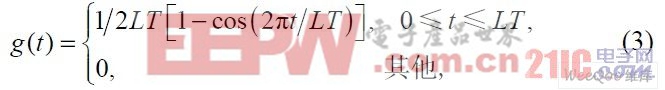

其中n I 是M (M = 2,4,8,16……) 进制的符号信息,取值为{±1,±3,……,±(M -1)}。文中M 为二进制调制, n I 的取值为+1、-1。h 是调制指数,g(t)是成形脉冲函数。脉冲函数g(t)采用升余弦脉冲RC:

式(3)中, L 又称为关联长度。

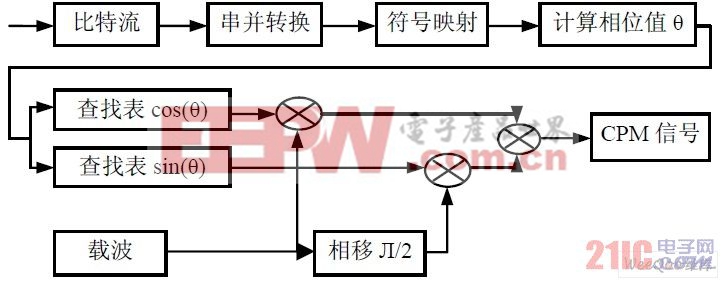

根据式(2)计算CPM 信号的基带相位,根据相位计算基带信号的I/Q 两路,之后使用两路信号相加就可以得到调制后的CPM 信号,见图1。

图1 CPM 信号调制

评论