基于FIash和JTAG接口的FPGA多配置系统

摘要:针对需要切换FPGA器件的配置以实现不同功能的特殊应用场合,提出了一种使用大容量的Flash存储器作配置码流载体的FPGA多配置系统。该系统采用传输速度快的JTAG接口提高了配置码流的烧写速度,采用并行从模式减少了FPGA器件配置时间,并利用串口通信实现了配置码流的在线切换。应用结果表明,该系统操作方便,可靠性高,实现成本低,通用性好。

关键词:FPGA;Flash存储器;JTAG

引言

针对需要切换多个FPGA配置码流的场合,Xilinx公司提出了一种名为System ACE的解决方案,它利用CF(Compact Flash)存储卡来替代配置用PROM,用专门的ACE控制芯片完成CF卡的读写,上位机软件生成专用的ACE文件并下载到CF存储卡中,上电后通过ACE控制芯片实现不同配置码流间的切换。

System ACE的解决方案需要购买CF存储卡和专用的ACE控制芯片,增加了系统搭建成本和耗费了更多空间,而且该方案只能实现最多8个配置文件的切换,在面对更多个配置文件时,这种方案也无能为力。但若要开发System ACE的替代方案,则需要选择更合适的可反复编程存储器,并且需要选用合适的传输协议接口来下载配置码流。通过串口或并口来下载配置码流速度太慢,不能满足应用中快速下载的需要;通过USB接口来下载配置码流则需要专门的控制芯片,增加了系统设计的成本。

本文选用大容量NOR Flash存储器来存储配置码流,并利用JTAG接口完成配置码流下载的FPGA多配置解决方案。与System ACE方案相比,该方案不仅能快速完成多个配置码流的下载,还具有更高的配置速度和更低的实现成本。

1 JTAG接口模块的设计

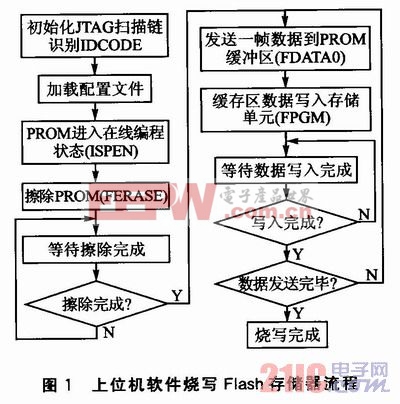

为了将配置码流写入Flash存储器,上位机软件通过JTAG下载线与JTAG接口模块连接。JTAG接口模块接收上位机软件发送的JTAG信号,从中提取出JTAG指令及对应的数据,并产生针对Flash存储器的擦除和烧写信号。由IEEE 1149.1—2001标准以及NOR Flash存储器先擦除后写入的特性,设计上位机软件的具体执行流程如图1所示。同时为了完成Flash存储器的擦除和烧写,本文在软件设计中规定了一系列的自定义JTAG指令,如图1中括号内所示。本文规定一帧数据大小为4 096比特。

评论