基于FPGA和TFT彩屏液晶的便携示波器设计

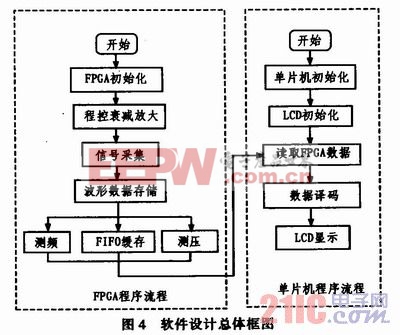

3 系统软件设计

系统软件设计主要完成对程控衰减放大电路的控制,时基的选择,异步FIFO设计,FPGA与单片机的通信协议设计,波形参数测量以及波形显示中的触发设置等。软件设计总体框图如图4所示。本文引用地址:http://www.eepw.com.cn/article/191214.htm

3.1 异步FIFO设计

A/D采样得到采样数据的数据率很高,为了保证单片机读取数据的有效性和可靠性,系统中使用异步FIFO对数据进行缓存。FIFO的设计是通过配置FPGA内部的BlockRAM资源实现的。为了实现边采集边显示的目的,配置两块相同的FIFO,在读写时钟的控制下,通过读使能和写使能信号的设置,使得在同一时刻始终有一块FIFO在进行写操作,而另一块FIFO在将写满的数据读出。而对于同一块FIFO不允许读写信号同时有效,这样接收A/D数据和读取数据并交给单片机处理可以同时进行,从而保证数据传输的连续性。

3.2 FPGA与单片机通信的实现

FPGA与单片机之间有效的通信是系统实现正常功能的重要前提,系统中通过数据总线,地址总线和控制总线将两个模块联系起来。在FPGA中,将不同类型的数据存放到不同的地址中,这些数据包括实时采集到的波形数据,测量得到的信号参数(电压和频率),当前的时基、垂直分辨率以及一些控制参数。单片机通过地址总线对FPGA的内存进行访问,并对读取的数据做出相关的译码处理,并将处理结果实时显示在液晶屏幕上。

控制总线包括读使能和写使能信号,分别控制异步FIFO的读写操作。当其中一块FIFO中存够指定数量的采样数据以后,读使能信号有效,单片机开始接收数据,此时另一块FIFO开始写入采集数据。当数据接收完毕后,单片机向FPGA发出写使能信号,此时两块FIFO交换功能,单片机控制LCD将波形实时显示出来,并以此循环交替工作。这种异步总线握手协议的设计,使得单片机的读和FIFO的读写协调工作,大大提高了数据传输的可靠性。

3.3 波形参数的测量和触发嚣的软件实现

对信号参数的测量是示波器的重要功能,本系统可以测量输入信号的频率和电压。在FPGA内利用等精度测频技术和比较法分别进行测频和测压,由单片机通过地址线读取数据并完成数据的译码和显示。

触发器是示波器的重要组成部分,通过触发器产生的控制信号,控制示波器对波形数据的存储和显示,达到稳定同步的目的。本系统设计的触发器,采用全数字化结构,大大降低了系统硬件电路的复杂性,并且触发条件的调整比较方便。触发器通过引用单片机内部的RAM资源定制了一个采集数据的缓存区,将波形数读入该缓存区,按照预先设定的触发门限,将缓存区中的数据读出,如果满足触发条件,则将数据在屏幕上显示出来。

4 系统调试和测试

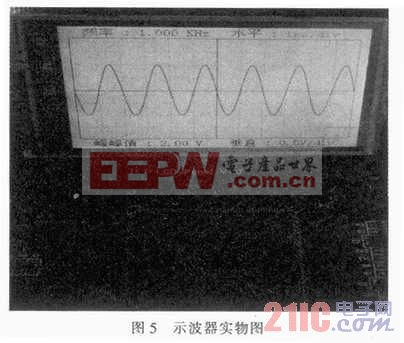

在完成了系统的硬件设计和软件设计以后,需要进行综合调试和测试。通过调试,不断优化程序代码,使系统的性能得以提高,工作状态更加稳定。在进行测试时,输入峰峰值为2 V,频率为1 kHz的正弦信号,在LCD上观察到的波形及测量参数如图5所示。从图中可以看出,波形显示稳定连续,测量信号参数的精度高,且包含彩色信息丰富。

5 结束语

研究了以TFT彩屏液晶作为显示器件的手持数字存储示波器的总体方案,即信号调理电路,核心采集模块,单片机处理模块和液晶外围电路组成。在确定总体方案的同时,给出了实现此总体方案的具体方法。

通过握手协议合理解决单片机与FPGA通信的问题,用软件设计了数字触发器,取代了一般示波器中常用的触发电路,降低了系统的硬件复杂度。该数字存储示波器允许输入信号的动态范围大,体积小,便于携带,操作简单,具有很高的应用价值和广阔的发展空间。

评论