基于FPGA的多功能密码锁的设计

摘要:本文设计的基于FPGA的电子密码锁,具有记忆和修改6位密码、输入密码位数指示及防止多次试探密码等功能,与银行卡的原理和功能极其相似,使得密码锁的保密和安全性能进一步增强。最后,给出了在Quartus II软件开发平台上实现密码锁各项功能的仿真图,并在FPGA芯片EP1K30TC144-3上通过了验证。

关键词:现场可编程门阵列;超高速集成电路硬件描述语言;密码锁

0 引言

电子密码锁能保护用户的重要资料不被非法用户所窃取,目前使用的电子密码锁大多以单片机为控制器,通过运行程序完成密码锁的各项功能。由于受到外部干扰的影响,单片机很容易将程序“跑飞”,因而可靠性较差。仿照银行卡输入密码的原理,本文介绍了一种基于FG-PA的多功能密码锁的设计和实现方案,由于采用纯硬件实现,使得可靠性和安全性大大提高。

1 电子密码锁的功能要求

设计的密码锁至少具有下列功能:

(1)6位密码,与银行卡密码位数相同;

(2)每位密码采用十六进制数,与十进制数密码相比,密码被破译的概率大大降低;

(3)每位密码按下时,有密码位数指示,类似自动取款机输入密码时有“*”号提示;

(4)密码输入过程中密码有误时,能对已经输入的密码清除以便重新输入密码;

(5)6位密码输入都正确后,应有开锁指示,上锁时也应有上锁指示;

(6)密码连续三次输入错误,密码锁死锁,并开启报警,防止窃贼多次试探密码;

(7)初始密码默认为“123456”,密码可以修改,在密码锁打开状态下,再一次输入正确的旧密码及两次输入的新密码一致时,密码才能修改成功。

2 密码锁的系统构成

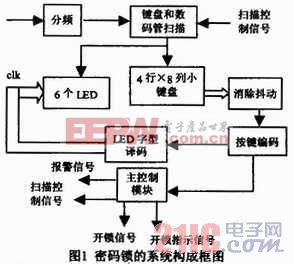

根据密码锁具有的功能,可将其实现的功能划分成分频模块、键盘和数码管扫描模块、按键抖动消除模块、按键编码模块、键值到7段数码管译码显示模块和主控制模块等6个子模块,如图1所示。

(1)分频模块。它对系统的主时钟进行分频,以产生4×8小键盘的列扫描信号和6位数码管的列扫描信号所需要的时钟。分频是因为消除按键抖动的计数器时钟要比分频后扫描时钟高得多。

(2)键盘和数码管扫描模块。它检测到分频输出信号的上升沿到来时,就对扫描的列加1,当扫描到最后一列即第7列,再从第0列开始扫描。当检测到有键按下的扫描控制信号时,则停止列扫描,直至按键释放后,再接着扫描下一列。数码管的6列扫描信号和小键盘的8列扫描信号可以共用,当扫描到小键盘的第6、7列时,并没有扫描6位数码管,由于扫描速度足够快,这并不影响数码管的动态显示。

(3)按键抖动消除模块。机械键按下时,会产生抖动现象,若不消除,一次按键会被错误地认为同一键被多次按下,从而造成无法正确地输入密码。消除的方法可以采用硬件方法如RS触发器和软件延时方法,本文采用后者。

(4)按键编码模块。它负责将按下键的行列位置码编码成0~31的键值码,键值0~15当作有效的16进制数输入密码位,大于等于16的键值可以定义成功能键,如定义清除密码键[Clear]键值为17,确认键[Enter]键值为23,修改密码键[Chgsecret]键值为24,其他没有定义的键可

以预留升级时的备用功能键。

(5)译码显示模块。它负责将按下的数值键0~F译码成7段LED共阴极字型码。

(6)主控模块。它依据消除抖动后产生的按键释放信号koff及按下的是数值键或功能键决定转移的下一状态,在不同的状态完成密码的比较、修改及多次试探密码报警提示等多项控制功能。

3 软件实现

本文采用VHDL语言实现本密码锁系统的设计。对系统中划分出的每一个模块功能都可以采用一个进程来描述。分频、扫描和译码显示三个功能模块都比较简单,本文只重点介绍剩余的3个模块实现原理及进程中的部分关键代码。完整的代码可以向本文作者发邮件索取。

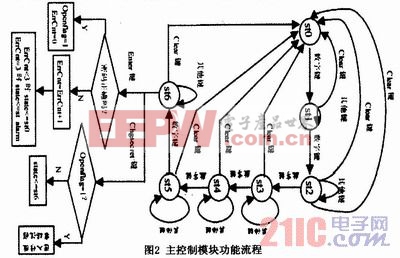

根据主控制模块实现的功能,可以整理成如下图2所示的流程图,图中对修改密码的流程作了省略。

评论