基于CORDIC算法2FSK调制器的FPGA设计

通过频率控制字,改变相位累加器的步长,这样即可改变正弦载波的频率。具体的数学推导如下:

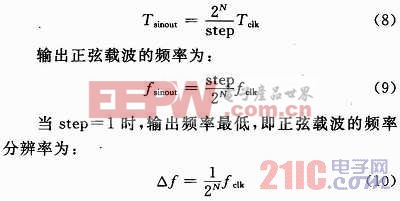

设相位累加器的字长为N,频率控制字即步长为step,则2N就相当于2π rad,N位中的最低有效位相当于2π/2N rad,即最小的相位增量,step对应的相位为step×(2π/2N)rad,完成一个周期的正弦载波输出需要2N/step个参考时钟周期。所以输出正弦载波的周期为:

可见改变相位累加器的步长step,可以改变正弦载波的频率;改变相位累加器的字长N,可控制正弦载波的频率分辨率。在相位累加器后加入相位加法器,通过改变相位控制字P,可以控制输出信号的相位;通过设置幅度控制字A,可控制最终输出的正弦载波的幅度大小。因此,通过对相位控制字、频率控制字或幅度控制字进行多路选择,可以形成不同进制的调制方式。可以看出,使用该结构可以很容易实现频率调制、相位调制和幅值调制。

3 2FSK调制器的FPGA设计

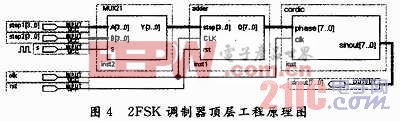

图4为2FSK调制器顶层工程原理图。该原理图主要由三个模块组成:2选1数据选择器MUX21、相位累加器adder、正弦载波生成模块eor-dic。其中,clk为系统时钟信号,rst为系统清零信号,step1,step2为2个不同的频率控制字,s为系统频率控制字选通端。2选1数据选择器的选通端s受基带信号控制,当基带信号为‘0’时,选通控制字step1;当基带信号为‘1’时,选通控制字step2。通过对step1,step2的选择,可以实现频率的切换。本文引用地址:http://www.eepw.com.cn/article/191186.htm

在QuartusⅡ环境中,三个子模块均用VHDL语言进行设计,系统顶层工程采用原理图进行设计,对系统顶层工程进行器件选择、引脚锁定、编译、综合后下载到Cyclone系列EP1C12Q240C8器件中,通过在频率控制字的引脚选择不同参数即可在FPGA器件中完成2FSK调制器的设计。

4 系统硬件实时测试

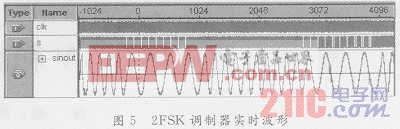

调制器的输出信号为数字信号,经D/A转换后可以通过示波器进行测试,也可以直接采用QuartusⅡ软件中的嵌入式逻辑分析仪Signal-TapⅡ进行测试。

采用SignalTapⅡ进行芯片测试,用户无需外接专用仪器,就可以对FPGA器件内部所有信号和节点进行捕获分析,而又不影响原硬件系统的正常工作。经测试得到的实时波形如图5所示。测试结果表明,基于FPGA和CORDIC算法的2FSK调制器设计方案是正确可行的,且波形流畅,在转换处能快速进行切换。

5 结语

用FPGA和CORDIC算法实现信号调制,既克服了传统方法耗费资源、运行速度低等缺点,还具有静态可重复编程和动态在系统重构的特性,极大地提高了电子系统设计的灵活性和通用性,大大缩短了系统的开发周期。

评论