降低CPLD的功耗的嵌入式应用

2.5 选择逻辑门

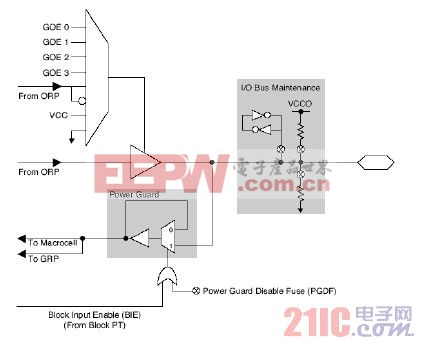

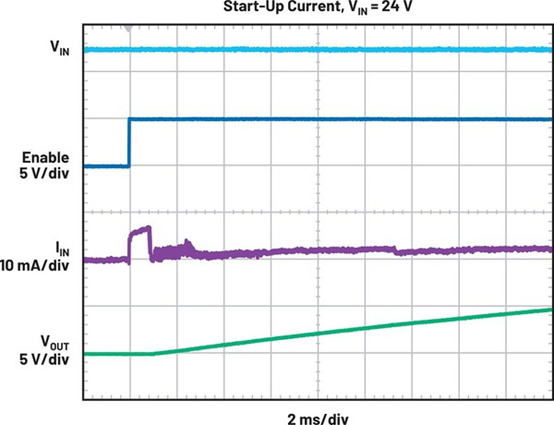

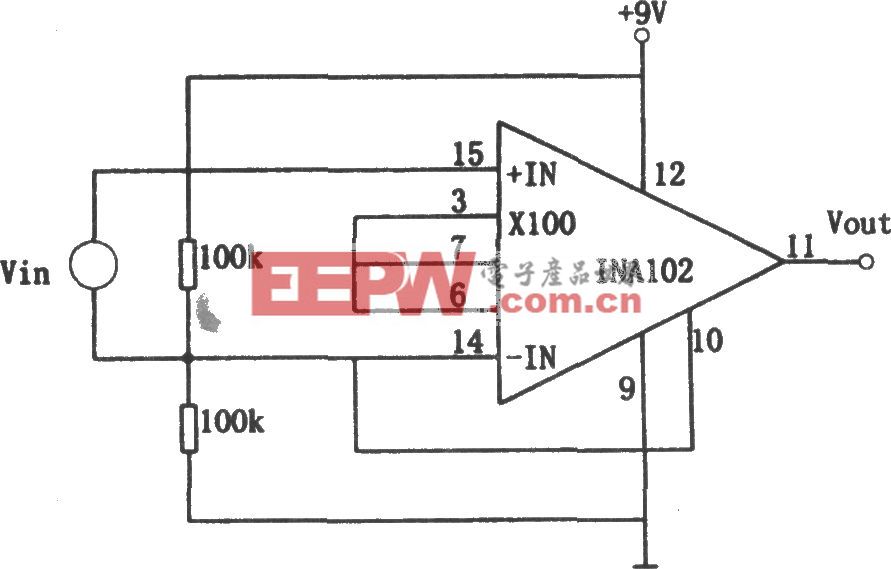

如同大多数的CPLD,ispMACH 4000ZE具有一个功能(莱迪思称为“Power Guard” 功耗卫士),当它们不需要相关的逻辑时,可禁用单独的输入。主机处理器、其他的外部逻辑,或CPLD的其他部分可以使用器件的块输入使能线,以保持CPLD的逻辑选定的块被时钟控制(图4)。例如,如果CPLD的某个部分被用作解码器电路,只有该功能正在使用时,主处理器可以使它能工作,使之能够在其余的时间保持休眠状态。

图4 Power Guard电路

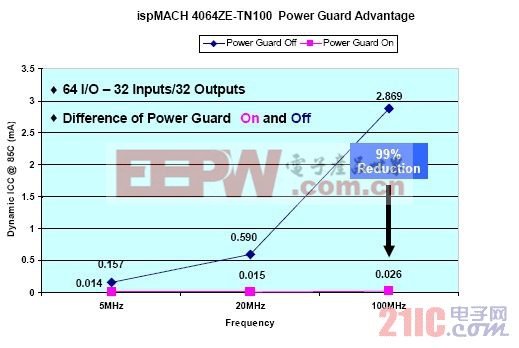

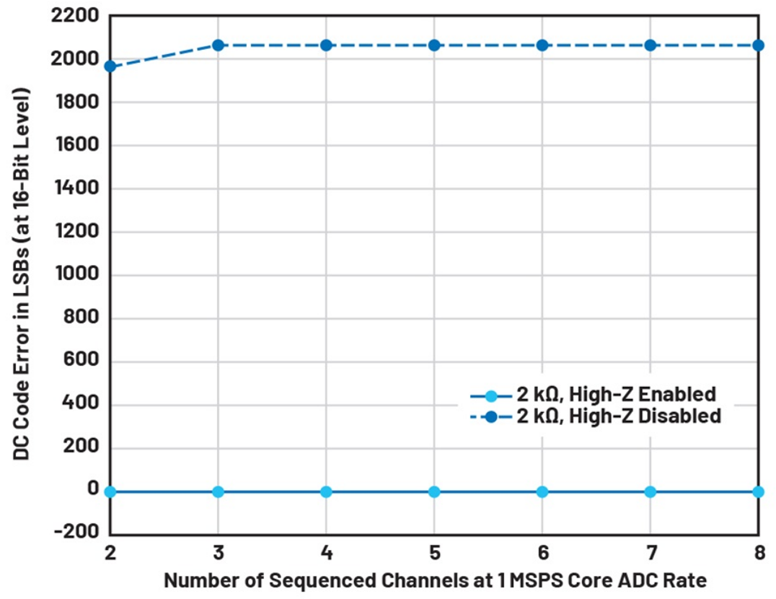

根据实际的应用使用Lattice的Power Guard或其他方法来禁用时钟至选定的CPLD的输入引脚,这样可以大大降低动态功耗。尤其是如果逻辑信号的时钟频率超过30兆赫时,这些方法特别有用。图5说明了可以用选择逻辑时钟技术实现潜在的节省功耗的方法。

图5 Power Guard 节省的功耗

3 针对低功耗的I/O设计

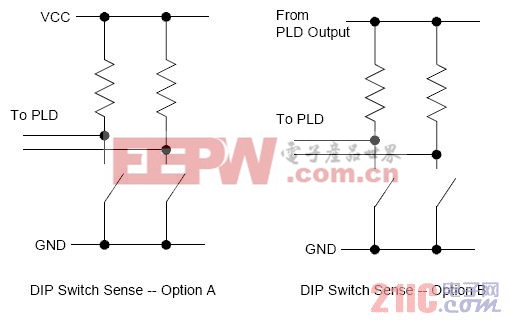

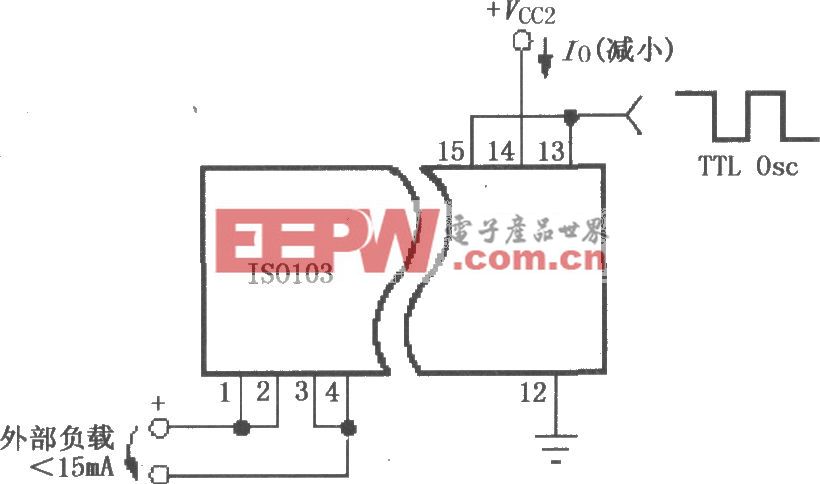

除了使用已经阐述的技术,目前大部分项目给予精明的工程师更多节省多余的微瓦功耗的机会-如果他们愿意关注潜伏在许多设计中的微小能源汲取部分。一个好的例子是无处不在的为开关提供读出电压的上拉电阻,以及连接到CPLD的输入线(图6)。通过使用CPLD的输出,或其他控制线至电源电压到读出线,只有当他们被读取时,并且读出线接地时,设计人员方可去除这个小而稳定的电流。

图6 无源和有源功率开关读出线

4 结语

大多数基于CPLD设计至少包括一些未引起注意的角落,在这些地方潜伏着耗能大户,他们悄悄地汲取电池的能量。幸运的是,认真实施一些重要的原则可以制止这些讨厌的寄生部分。当选择CPLD和其他元件时,注意其静态和动态功耗等级:他们随供电电压、温度和工作频率而变化。同样要注意“最小”、“最大”和“典型“功耗指标,它们将影响你的设计。尽量减少CPLD的偏置电流,确保其待机配置不与其他与之相连的器件相冲突,关闭任何不必要的内部功能。

管理动态功耗,只给当前CPLD需要的部分加时钟。莱迪思的Power Guard功能提供一个简单的方法来选择关闭时钟至专门的输入,如果无法使用的话,还有其他的技术可用。使用精确的电源控制驱动逻辑,可实现节省额外的动态功耗,使用尽可能低的电源电压。检查I/O的连接,看看是否有不必要的可去除的加载的汲取功耗的上拉/下拉电阻,或只在需要时才选择加载电阻。

如果你仔细地将这些工具应用到下一个项目,设计中就不会有隐藏的汲取功耗的大户,你的产品将会有很长的寿命哦!

评论