降低CPLD的功耗的嵌入式应用

2.1 设置偏置电流

通过选择合适的器件可以控制CPLD的泄漏电流,现在到了运用你的工程技能调整偏置电流的时候了。用来管理偏置电流的技术大致分为两种类型:

确保CPLD的待机配置不与上拉/下拉或相关的其他器件所用的总线驻留技术相冲突;动态控制内部功能块(如振荡器),使他们只开启所需要的部分。具体取决于所使用的CPLD,这是增加更多的待机时间到设计中的好方法。

2.2 并行驻留101方案

在许多设计中,嵌入式主处理器可以使用自己的总线驻留方案,以保持在总线或I/O上所需的逻辑电平,所以你只须为CPLD的待机模式做准备,确保其激活总线的管理功能被禁用。在其他应用中,总线上其他地方的上拉或下拉电路也可以缓解在待机期间CPLD必须管理总线的情况。

但是,不需要CPLD做任何事情并不意味着你也不需要做任何事情。花些时间验证只有一个设备驱动总线是一个重要的任务,因为单个引脚上的逻辑冲突可导致待机功耗为整个芯片标称值10uA 闲置功耗的2~15倍。

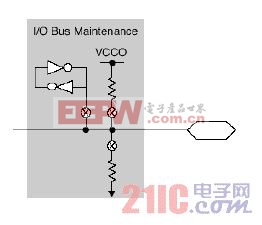

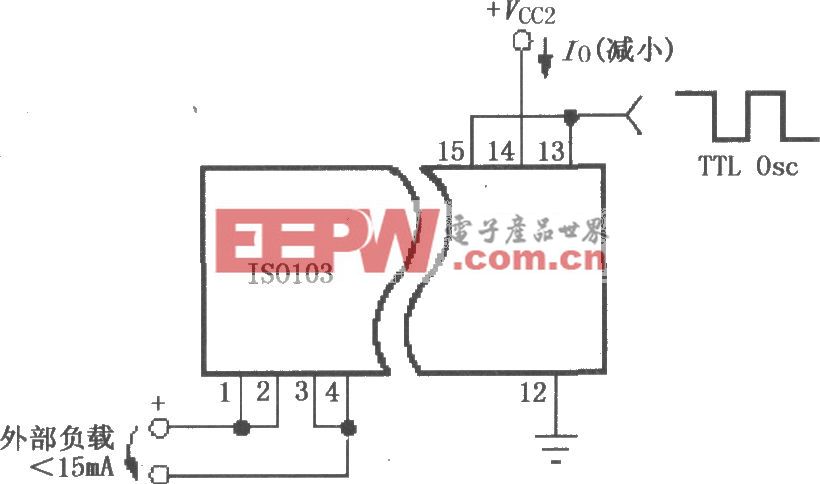

在主总线驻留机制无法使用情况下,可以使用上拉/下拉,以及在大多数现代的CPLD中拥有的总线保持功能。如同大多数同类器件,莱迪思的ispMACH 4000ZE CPLD的I/O引脚都配备了可选的上拉和下拉电阻,在待机状态(图3)可提供合适的逻辑电平。4000ZE系列还配备了节省功耗的总线保持功能(也称为总线保持):一种弱激活驱动电路可设置为激活或零,同时产生比简单的电阻器消耗小得多的功耗。一点忠告:虽然总线保持功能可大大节省功耗,但必须肯定它是唯一的在线有源器件,否则会有吸入大电流的风险。

图3 CPLD的总线管理选择

2.3 动态功耗管理

设计人员需要关注两种类型的动态功耗。运行功耗预算的第一部分是CPLD需要实际工作时的那部分。管理策略的其他部分涉及关掉输入至此刻不需要的CPLD的部分,阻止它们切换,或在可能的情况下将它们全部关闭。

2.4 精密的电源管理

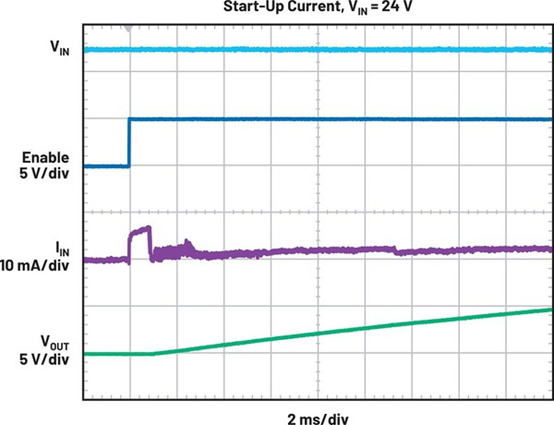

虽然CPLD逻辑的许多部分很可能被连续使用,在有意义的时间段内不能禁用,因此使用低电源电压仍然可以节省功耗。由于功耗是电压平方的函数,用1%的精确开关稳压器,可让设计运行于CPLD工作范围的下限,您可以节省相当多的功耗。例如,如果一个标称值为1.8V的CPLD工作在1.65V,它大约少消耗30%的功耗,这还不包括在较低Vcc的情况下泄漏电流的减少。

评论