如何提高基于FPGA的原型的可视性

采用基于现场可编程门阵列(FPGA)的原型的验证团队面临的最大挑战之一在于当原型系统未能发挥期望的性能时了解原型系统的内部行为。分析和调试这些设计的一个关键因素是难以观察内部信号。

本文引用地址:http://www.eepw.com.cn/article/191087.htm目前的顶级FPGA在容量和性能方面均提供巨大的能力。例如,Xilinx Virtex-5家族成员包含成千上万可以配置成逻辑、RAM或移位寄存器的逻辑单元。此外,这种可编程逻辑可与硬IP块搭配使用,如工作频率全部高达550MHz的兆位RAM以及数百个25×18乘法器/DSP功能。

这些可能还包含多个硬和/或软处理器内核和相关外围器件的设备可以用作ASIC和片上系统(SoC)元器件的功能强大的原型平台。

新工具、改进的方法以及更高的抽象级正在帮助工程师实践不同的宏架构和微架构,并帮助他们提高其总设计生产力。

对于验证而言,这些设计的绝对规模和复杂度再加上大幅增加的软件内容使得FPGA原型对于通过硬件加速提高验证吞吐能力以及提供一个早期的软件开发平台都是一个极具吸引力的选择方案。但是,成功的原型要求当设备无法按预期工作时对发生的状况和工程师必须调试的对象予以应有的考虑。

如上文所述,分析和调试原型设计的关键因素在于难以观察内部信号。问题在于可能有成千上万个这样的信号,但是这些信号可能仅通过设备上的有限个输入/输出(I/O)引脚暴露在外界。

此外,观察内部信号的操作会影响设计和验证。选择要监视的合适信号是一个并不琐细的任务,修改设计以观察这些信号会耗费工程和FPGA资源。同样,捕获、转出和记录要观察的信号值也要花时间。

访问和分析FPGA内部信号的任务复杂、繁琐而耗时,这取决于所用的方法。话虽如此,不过总过程也可以分成五个主要步骤:1. 确定一组要观察的信号;2. 修改设计,以观察所选的信号;3. 当FPGA在原位工作时观察并找回数据;4. 将找回的数据映射至最初的RTL表示法;5. 计算不在最初观察的信号组中的其它信号的数据。

本文首先讨论与执行这些活动有关的现有技术的局限性。然后介绍新兴的可视性增强技术;这种新的技术包括一组缩减的要观察的信号的自动交互选择以及填充“遗漏片段”(未观察到的信号值)的“数据扩展”技术。

传统技术的局限性

就像刚才提到的,采用传统技术定位、分析和调试FPGA中的问题可能极其繁琐和耗时。其中的原因可以简单地进行总结。

这个过程的第一步是决定哪些信号需要进行观察(捕获和转出)。但是要观察的信号量的增加会增加捕获信号所需的逻辑资源以及将其数据值传达给外界所用的时间。由于这些原因,因此可能只能在特定时间(即特定的验证运行)观察有限个信号。

这里的问题在于选择要监视的最佳信号是一个并不琐细的任务。例如,看起来是监视的最佳选择的寄存器可能实际上只能为设计的操作提供有限的可视性。相比之下,表面上无害的寄存器可能为设计提供极高的可视性。

一旦选定一组要监视的信号,必须对设计进行修改以便允许直接观察信号,或者允许捕获信号并将其转出到外界。广义上讲,这叫可调试性设计(Design-for-Debug,DFD)。在以前的技术案例中,设计可以通过多路复用器和控制逻辑进行扩展,多路复用器和控制逻辑可以用来通过主要输出引脚来将所选的内部信号呈现到外界。一般而言,这种技术实现往往是一种内部的专门技术,这些实现需要大量工作来有限地了解芯片内部正在发生的状况。

替代技术是采用内部逻辑分析仪(ILA)。这些分析仪可能是内部技术,但是FPGA供应商或专业的第三方供应商一般都提供这些分析仪(以及相应的配置应用)。每个ILA都是采用可配置逻辑单元和RAM区块的组合而构造的。ILA的控制逻辑被设计成允许特定的触发条件(或组合的触发条件)开始捕获一个或更多特定信号并将与这些信号相关的属性(如数据值和时间戳记)存储在片上内存中。在某个阶段,这些值必须被转出到外界。这种情况下的一般技术是采用芯片的JTAG端口。

设计你自己的ILA不仅耗时而且费力。事实上很难确定是自动调试设计的还是ILA在调试设计。甚至在使用FPGA供应商的经过验证的鲁棒ILA时,每次选定要监视的一组新的信号时仍然需要对设计进行重新编译。重新编译的工作可能要花几个小时,因此最好最大限度地减少需要执行这个任务的次数。

在设计修改和设计重新编译阶段之后,进行验证运行,并捕获来自内部信号的数据。为了让这些数据可用于下游调试工具,数据必须包含特定的属性。除了数据本身的逻辑值之外,数据必须包含信号的完整分层实例名以及每个数据转换的相对操作时间(时间戳记)。此外,转出数据的文件格式应为工业标准,如VCD或FSDB。

在专有解决方案案例中,有必要将这些属性添加到信号数据流和/或将内部格式转换成其对应的工业标准格式。幸运的是,FPGA供应商和专业供应商提供的ILA一般捕获必需的数据并使用工业标准格式。

从ILA收集的数据通常与FPGA的门级视图有关。但是设计工程师更熟悉设计的RTL表示法。因此,为了为调试过程提供便利,有必要将门级实例映射成RTL视图。这并不像听起来那样简单,因为大多数情况下,门级实例和RTL视图之间并没有一一对应关系。许多传统的内部解决方案都无法提供这种能力。

验证运行之后,访问和分析其它信号以对问题进行跟踪始终都是有必要的。当采用传统设计流程时,设计工程师必须返回上述五个步骤中的第一步。即,他们必须选择一组新的信号、修改设计并对其进行重新编译、执行新的验证运行、将新数据映射至RTL,然后分析结果。这个过程必须重复多次。

可视性增强技术

为了解决传统FPGA原型调试环境的局限性,出现了一种为设计的内部工作提供增强可视性的技术。为了达到完全的效果,可视性增强工具和技术必须应用于流程中的每一个步骤。

如上所述,过程中的第一步是确定哪些信号需要观察。根据系统展示的不正确输出,设计工程师通常对相关的一个或多个功能区块有“感觉”。例如,内存控制器和/或总线仲裁器区块。

作为单靠经验和实践的方法,你需要能够观察区块(通常为寄存器、内部内存定位和区块的主要输入/输出)内部大约15%的信号。这将在本小节后面讨论的自动数据扩展技术环境中提供95%~100%的可视性。

遗憾的是,资源限制不允许捕获所有这些信号。在这种情况下,选择为振动提供最佳碰撞的信号显然是更可取的。因此,可视性增强信号选择包括“影响能力”的概念,即每个信号影响的下游逻辑的量。为了确定调试所选区块所需的基本信号最小阵容,你将必须分析断言、RTL或门级网表代码,有时这三项都需要关注以*估影响能力。例如,为了调试断言故障,可视性增强信号选择将分析设计和所选的断言,以抽取调试每个断言所需的最小的一组信号。

此外,如果设计工程师对他们希望观察的一组信号进行了明确的定义(这样的选择可以在RTL和/或门级网表中进行),可视性增强信号选择工具将自动识别任何寄存器、内存元件以及观察指定的内部信号所必须捕获的主要I/O。

一旦选定一组要监视的信号,可视性增强环境将自动与FPGA和/或第三方工具供应商沟通,以通过增加适当的ILA来修改设计。在没有足够的资源捕获所有所需信号的情况下,可视性增强环境将以被认为具有更多上述影响能力的信号作为其选择的基础。

在执行验证运行时,可视性增强环境将自动记录和/或提供下游分析和调试环境所需的所有信息;该信息将包括逻辑值、信号的完整分层实例名以及数据转换的相对操作时间。此外,转出数据文件的格式将为工业标准格式,如VCD或FSDB。

正如上文指出的,从ILA收集的数据通常与FPGA的门级视图有关。为了了解这种门级逻辑中发生的状况,工程师必须使门级数据与设计的RTL表示法相互关联,甚至与系统级描述相互关联。

但是,由于合成和优化的原因,并非门级表示法中的每个信号均有RTL表示法的相应信号。为了解决这个问题,可视性增强环境必须以某种方式地方化信号相关性。其中一个方法是自动生成结构依赖图像并采用近似的图像匹配算法。这个方法模仿人类使用的过程,人类通常通过查看扇入区和扇出区中的寄存器来定位相应区域。

或许可视性增强最重要的方面在于其动态数据扩展能力。但是这种能力依赖于所有上述要点,特别是可视性增强信号选择。选择要观察的信号的宗旨就是为了便于自动数据扩展。

以下是数据扩展的思路。通常,设计工程师可能希望显示和分析不在被捕获的信号组中的信号。较可取的做法是插入遗漏的数据,而不倾向于修改设计和执行新的验证运行。因此,可视性增强环境将通过数据扩展来填充捕获数据中遗漏的间隙。

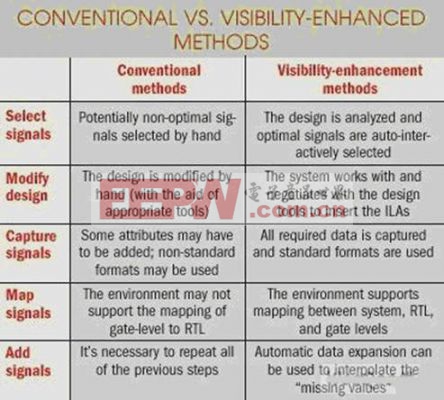

特别地,这种数据扩展可以填充位于信号被捕获的寄存器之间的组合逻辑区块内部的信号。为了最大限度地提高性能,只对进行试验的逻辑进行动态的数据扩展,而不是对所有设计逻辑进行静态的数据扩展。传统设计环境与其可视性增强环境的对比如表所示。

可视性增强技术可以极大地加快定位、隔离和了解基于FPGA的原型中的错误症状原因的过程(类似的技术可以应用于基于FPGA的仿真和软件仿真中)。

在一般的设计中,寄存器约占信号的20%。采用可视性增强技术允许设计工程师将这些信号作为确定余下80%信号的值的基础,这相当于可视性提高了大约五倍。而据使用这种技术的用户报告,调试时间减少了四倍。换言之,在不使用可视性增强技术的情况下调试所用的每一个小时在使用该技术之后都可以缩短至仅15分钟。

就未来而言,可视性增强环境提供的数据扩展能力为将内部FPGA信号数据与一般只在软件仿真环境下考虑的先进调试技术搭配使用提供了基础。例如,如果设备包含复杂的内部总线,扩展的数据可能会在事务级被查看,从而使了解设备的操作更加容易。在调试器环境中谨慎地集成数据扩展技术可以同时缩短验证运行时间和最终的捕获数据文件大小。这种环境将实现自动化向导调试以及先进的分析和跟踪能力。

本文小结

使用基于FPGA的原型的设计和验证团队所面临的最大挑战之一是当系统未能按期望执行时了解系统的内部行为。可视性增强验证和调试环境通过以下方式解决了这个问题:帮助选择要观察的信号;与其它工具配合工作(和协商),从而对设计进行修改以捕获所选的信号;捕获所有驱动下游工具必需的数据和属性;使用先进的技术在系统、RTL和门级视图之间自动映射;执行数据扩展以填充未被捕获的信号的值。

评论