基于FPGA的汉明距离电路的实现

摘要:FPGA既具有门阵列的高逻辑密度和高可靠性,又具有可编程逻辑器件的用户可编程性,可以减少系统的设计和维护风险,降低产品成本,缩短设计周期。文中给出了利用FPGA设计汉明距离的计算电路,同时给出与通过有效的芯片资源配置,恰当地选择存储器的总容量与加法器总数,来使整个系统的资源利用率达到最佳的实现方法。

关键词:数字技术;FPGA;汉明距离;芯片资源

当今时代已经成为信息化时代,而信息的数字化也越来越为研究人员所重视。数字化技术已经引发了一场范围广泛的产业革命,各种家用电器设备,信息处理设备都将向着数字化的方向变化。如数字电视、数字广播、数字电影、DVD等等,同时现在的通信网络也向着数字化的方向发展。随着数字化的发展,数字集成电路也得到了广泛应用。20世纪80年代中期,Altera和Xilinx分别推出了类似于PAL结构的扩展型CPLD和与标准门阵列类似的FPGA,它们都具有体系结构和逻辑单元比较灵活、集成度高以及适用范围广等特点。同时,这两种器件也兼容了PLD和通用门阵列的优点,可实现较大规模的电路编程同时也很灵活。

汉明距离在信息论中的定义是两个等长字符串之间的汉明距离,也就是两个字符串对应位置的不同字符的个数。例如:*1011101与1001 001之间的汉明距离就是2;*2143896与2233796之间的汉明距离为3;*“toned”与“roses”之间的汉明距离为3。

在通信中,累计定长二进制字中发生翻转的错误数据位通常也被称为信号距离。事实上,汉明重量分析在包括信息论、编码理论、密码学等领域都有应用。

1 硬件设计

在扩频通信和数字突发通信系统中,接收机进行的数字相关检测或独特码检测,实际上就是本地一组确定序列的一位二进制数,接收机将接收到的数据连续不断的送入N位移位寄存器中,这样,任一瞬间移位寄存器中的内容即为一串二进制码,移位寄存器的输出作为ROM的地址输入,这样,经查找表运算后,ROM就可输出所需的数据,并将所得数据送入汉明计算电路以得到汉明距离,再经过门限判决输入的汉明距离。其汉明距离的计算电路框图如图1所示。

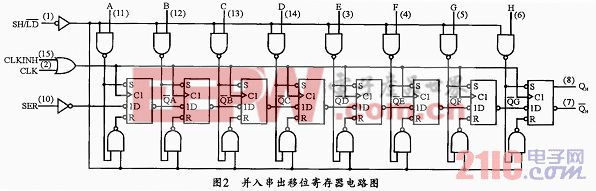

1.1 8位并入串出移位寄存器

图2是本系统中的并入串出移位寄存器电路图。图2中,当移位/置入控制端(![]() )为低时,并行数据(A—H)被置入寄存器;而当

)为低时,并行数据(A—H)被置入寄存器;而当![]() 为高电平时,并行置数功能被禁止。当CLK和CLK INK有一个为低电平且

为高电平时,并行置数功能被禁止。当CLK和CLK INK有一个为低电平且![]() 为高电平时,另一个时钟则可以输入;当CLK和CLK INK有一个为高电平时,另一个时钟被禁止:而只有在CLK为高电平时,CLK INK才可变为高电平。

为高电平时,另一个时钟则可以输入;当CLK和CLK INK有一个为高电平时,另一个时钟被禁止:而只有在CLK为高电平时,CLK INK才可变为高电平。

DIY机械键盘相关社区:机械键盘DIY

评论