基于FPGA的外部存储器设计

摘要:为了提高雷达海量数据的处理速度,采用FPGA设计了一种高速外部存储器,通过多次实验,验证了设计方法的可行性。高速外部存储器可以有效地提高数据存储速度,节约读/写时间,从而满足信号处理的高速实时的要求。这种方法充分利用FPGA设计方便,SDRAM和FLASH的存储读写速度快的优势,具有成本低廉,兼容性强,易于工程实现的特点。

关键词:雷达信号处理;FPGA;SDRAM;FLASH;存储器设计

0 引言

随着雷达技术的进一步发展,对雷达信号处理的要求越来越高,在实时信号处理过程中有大量数据需要存储,由于FPGA本身的存储器容量非常小,根本满足不了雷达信号处理过程中的需求,为解决这一问题,通过查询资料,引入SDRAM和FLASH作为FPGA的外部存储器。SDRAM存储器以其快速、方便和价格相对便宜,因而,常被用在雷达信号实时处理上。选择SDRAM而没有SRAM是因为SRAM价格太贵,SDRAM相对便宜。没有选择DDR SDRAM的原因是因为在实际的雷达信号处理中并不需要那么高burst率,SDRAM足以满足实际需求。SDRAM主要作用:在MTI处理时作为周期延迟器件、动态杂波图的存储和数据暂存等功能。虽然SDRAM有存储容量大、价格相对便宜等优点,但是其断电所有数据丢失的缺点,使其仅在FPGA外部连接SDRAM作为外部存储器件显然是不能满足设计需求的,因此,在设计过程中考虑到FLASH存储。在设计中用FLASH存储一些断电不能丢失的数据,如:脉冲压缩处理时的匹配滤波器系数、MTI处理时杂波加权系数、CFAR处理时的对数表以及一些函数求值等。

1 存储电路设计

1.1 SDRAM存储电路设计

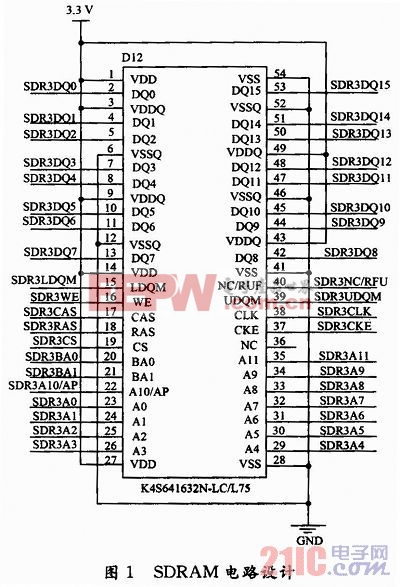

在硬件电路设计过程中,先通过SDRAM的I/O接口电平标准选择FPGA的外围I/O电平标准,从而解决电气互联问题。根据实时信号处理过程中所需的存储容量以及FPGA的型号,选择了4片SDRAM存储器,用于输入/输出缓存。芯片的型号为K4S641632N-LC/L75。SDRAM工作模式有多种,内部操作是一个复杂的状态机。SDRAM的管脚可以分为以下几类:控制信号,包括片选、时钟、时钟使能、行列地址选择、读/写选择、数据有效等。地址线行列复用,数据引线是双向传输。SDRAM的所有操作都同步于时钟,都是在时钟上升沿时控制管脚和地址输入的状态,进而产生多种需要的命令。

SDRAM与FPGA的连接,要把FPGA的普通I/O与SDRAM的除电源、NC和接地管脚之外管脚连接起来即可,所有的控制与工作时序都是由FPGA提供,由于管脚太多,采取了网络标号连接,其电路原理图如图1所示。由于篇幅关系,只给出了部分电路图。

评论