以FPGA为基础的SoC验证平台 自动化电路仿真侦错功

此外,观察额外的关键讯号是侦错时必需的,但这些讯号多半不在原始探测清单中。工研院工程师透过Probe Visualizer迅速的探测ECO流程,在10分钟内就可新增10个新讯号,而且不用重新编译整个设计。相对传统的侦错方法需要在RTL拖曳新讯号,并且针对这个特定的设计重新执行合成(synthesis )以及布局与绕线作业,约需花上2至3个小时,因此这方面的革新省下了大量的时间。

工程师能够轻松地将 所需额外的RTL探测讯号由Verdi侦错环境拖曳至Probe Visualizer。这套系统会自动建立RTL至逻辑闸层(RTL-to-gate level)的讯号对应关系,所以可直接在 FPGA 布局与绕线档案上迅速执行部份绕线作业来看到新增的探测讯号,大幅缩短侦错作业时间,所以能在短时间内处理多重侦错工作阶段 (debug session)。而对设计中使用的“黑盒子”IP区块,也只需EDIF名称,就可以进行探测ECO流程。

评估结果

工研院工程师在修正问题并成功试产设计之后,检讨了项目实际耗费的时间,并评估了这个新的FPGA SoC原型验证方法的成果。

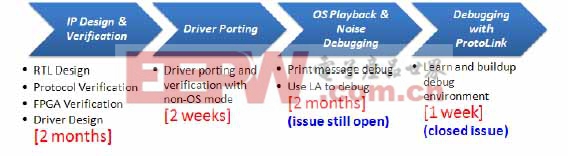

进行RTL设计、仿真、通讯协议验证与FPGA设计实现的时间约为2个月。在驱动程序移植(driver porting )上所花费的时间则短了许多,大约只有2个星期。工程师随后又花了2个月的时间进行验证作业,试图透过硬件逻辑分析器检查 FPGA 内部讯号解决音效问题,同时也在音效驱动程序中增加观察点,以连结并企图找出问题。这种传统的FPGA侦错方法,需要的时间和设计研发的时间一样长,然而对工研院团队而言,相当令人沮丧的是结果仍然一无所获。不过,在经过思源科技提供的应用软件教育训练/支持课程及一星期的实作经验后,工研院工程师使用ProtoLink Probe Visualizer,在短短一星期的时间内就厘清了两大问题!

对工研院而言,ProtoLink Probe Visualizer是一种相当有效的FPGA原型板侦错方法。工程师再也不必局限在传统的侦错方法,而且在实时应用软件中增加观察点也可能会造成其它问题。透过维持原有软件并监测更多FPGA讯号在数百万时脉周期内的实时RTL行为,使用者可以获得所需的能见度,更完美的掌握、更轻松地侦错设计的问题。

总合来说,思源科技Probe Visualizer透过以软件为基础的创新方法,改变了原型板验证的方法,实现丰富、实时的设计能见度,并且让原型板能使用Verdi的侦错威力,使原型板侦错时间比传统的方法大幅缩短一半。这种侦错作业生产力与整体验证效率的提升,不仅能协助工研院在更早期的SoC研发流程中配置FPGA原型,并且能迅速移转至搭载最新FPGA技术的新一代原型板上,充分运用最新FPGA技术的优势。

评论