基于FPGA直接序列扩频系统的设计

摘要 针对一般无线通信系统抗干扰、抗噪声以及抗多径性能力差的缺点,提出了一种基于FPGA的直接序列扩频系统设计。该设计采用63位的pn码作为扩频调制的码序列,在发送端,对信息码进行扩频调制;在接收端,对收到的扩频调制信号进行解扩,增强了系统的抗干扰性和可靠性。同时在Altera公司的QuartusⅡ软件中,使用硬件描述语言VHDL和原理图相结合的方法进行了电路的设计实现。通过把电路下裁到Altera公司的CycloneIII的EP3C10E144C8N芯片中调试,验证了扩频系统的可行性。

关键词 扩频;pn码;FPGA

由于扩频通信系统具有抗干扰性好、抗多径衰落能力强,可高精度测量、多址复用等优良特性,多年来得到了迅速发展和广泛应用。

1 直扩系统基本原理

直接扩频通信就是在发射端利用高速率扩频序列去扩展信息数据的频谱,包括伪码调制和载波调制这两个过程。与一般常见的窄带通信方式不同,主要体现在信息数据经扩展频谱以后成为宽带信号,再经过相关处理恢复成窄带信号后解调出信息数据,因此它具有信号相关处理和伪随机编码调制两大特点。

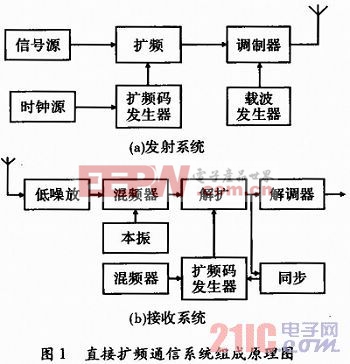

直接扩频通信系统组成原理如图1所示,在发端输入的信息先经信息调制成为数字信号,然后由扩频码发生器产生的扩频码序列调制数字信号以展宽信号的频谱。展宽后的信号再调制到射频发送出去。在接收端将收到的宽带射频信号,变频至中频,然后由本地产生的与发端相同的扩频码序列去相关解扩,再经信息解调、恢复成原始信息输出。

2 系统总体方案

在发射系统中,首先产生8位的串行信息码data_in,然后与来自pn码发生器的扩频伪码序列进行模2加,完成信号的频谱扩展,得到扩频信号data_kuo。在接收端经过pn码同步捕获后,将扩频调制信号与本地同步扩频序列进行异或运算,得到解扩信号data_jie,比较data_ kuo与data_jie波形图,从而验证系统扩频解扩的效果与可行性。

3 系统模块化设计

3. 1 信息码输入模块的产生

该模块功能是利用8位移位寄存器,在时钟信号的控制下移位输出8位信息码。clr为装载信号,当clr=0时,从拨码开关并行读入8位信息码,装入到内部8位寄存器中,当clr=1时,将输入的8位信息码在时钟信号的控制下实现串行移位输出。

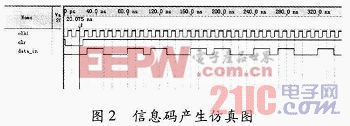

仿真结果如图2所示,扩频前的数据信息为11000110B。

评论