基于FPGA的电梯控制系统设计

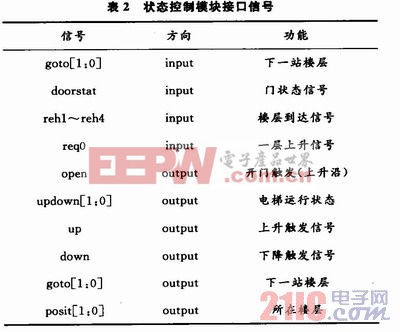

系统重启时(res=1),进入空闲状态(Idle),空闲状态下,输出信号posit=up=down=open=0,当输入信号goto为0时,保持空闲状态;当goto信号不为0时,进入上升状态(Stop)。当第一层上升信号触发时,进入停止状态。停止状态下,open信号上升沿触发电梯开门;up=down =0,posit=goto。在电梯开门延时期间(dooropen=1),保持停止状态;当电梯门关上时(dooropen=0),判断下一站楼层,若大于目前楼层,进入上升状态,若小于目前楼层,进入下降状态。上升状态下,up=1,updown=01,posit=goto,触发电机控制模块拖拽电机上升。楼层达到信号,使系统进入停止状态。下降状态同理。本模块接口信号如表2所示。本文引用地址:http://www.eepw.com.cn/article/190999.htm

模块3:电机控制模块

本模块输入信号有:上升触发信号(up)、下降触发信号(down)、所在楼层(posit)以及下一站楼层(goto),输出信号:4个位不同相位的电机驱动信号。模块由升降信号触发,经电机状态控制器,产生4个相位的电机驱动信号P[3:0],输出至电机驱动电路,其频率决定电机转动,其相位决定电机的转动方向。P[3:0]的各频率信号由分频器模块提供。

模块4:显示模块

本模块功能用于电梯所在楼层(posit)、电梯运行状态(updown)的七段码显示或LED显示。以及超载信号(over)的报警和显示。

模块5:门控模块

本模块用来控制电梯门状态,由输入门控信号open信号触发开门(doorstat=1),经过延时,电梯门自动闭合(doorstat=0)。所超载(over=1),则电梯门不合,电梯保持开门状态,直到超载信号清除。

模块6:分频模块

分频模块用来对系统时钟信号分频,产生向电机控制模块提供的各频率信号。

3 仿真验证

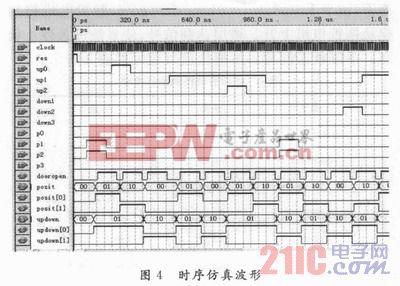

本设计顶层采用模块化设计,各模块采用VerilogHDL硬件描述语言。自顶向下的设计方式,便于程序查错、升级、改进,本设计稍加修改,即可实现任意楼层电梯控制。对所设计程序进行分析、编译、综合、布线后产生的电路进行功能仿真和时序仿真,均可获得符合设计要求的逻辑值。时序仿真波形如图4所示。

由图4可以看出:控制器始终能有效存储各楼层请求信号,能按照方向优先、循环次序执行各楼层请求。各信号状态符合设计要求。信号延时为10 ns级,在允许范围内。

本设计硬件实现采用康芯KX_7CH最小系统版。程序经引脚锁定并编程下载到器件,经测试,逻辑完全正确,达到设计要求。

4 结论

基于FPGA的数字电路设计方式在可靠性、体积、成本上的优势是巨大的,它已经成为实现数字电路的主要手段之一。本文设计的四层电梯控制器,稍加改进即适合于任意楼层,灵活性强,运行可靠,具有很强的适应性和实用性。

评论