便携式超高频RFID读写器的FPGA实现

摘要:设计了基于ISO18000-6C标准的USB2.0数据通信协议便携式射频读写器。以Altera EP1C3T144为核心控制器、CC1100为RF收发器、CH372为USB接口器件,组成了该硬件系统。经测试,系统收发频率为889 MHz,最高数据传输速率为240 kbps,天线发射功率为1.1 dBm,读写器稳定传输距离为1 m,数据传输准确,系统读写稳定可靠,抗干扰能力强,适用于各种复杂EMI环境。

关键词:ISO18000-6C;高频RFID;EP1C3T144;CC1100;CH372

引言

射频识别(Radio Frequency Identification,RFID)是利用微波进行双向数据传输的一种非接触式射频自动识别技术。RFID系统具有使用寿命长、低功耗、数据传输快速、稳定、安全、可靠,适应性和抗干扰性强等优点,已广泛用于工业控制、消费类电子、医疗电子、现代物流和校园一卡通等方面。RFID技术是现代物联网的核心技术。我国研究RFID技术起步比较晚,受软件和硬件等条件限制RFID技术还未真正实现大规模应用,大多数属于中、低频数据传输,距国外先进技术还有一段距离。本文重点介绍基于Altera公司Cyclone系列FPGA和ISO1800 0-6C标准超高频RFID读写器的软硬件实现方法。

1 系统原理和结构

1.1 RFID系统原理

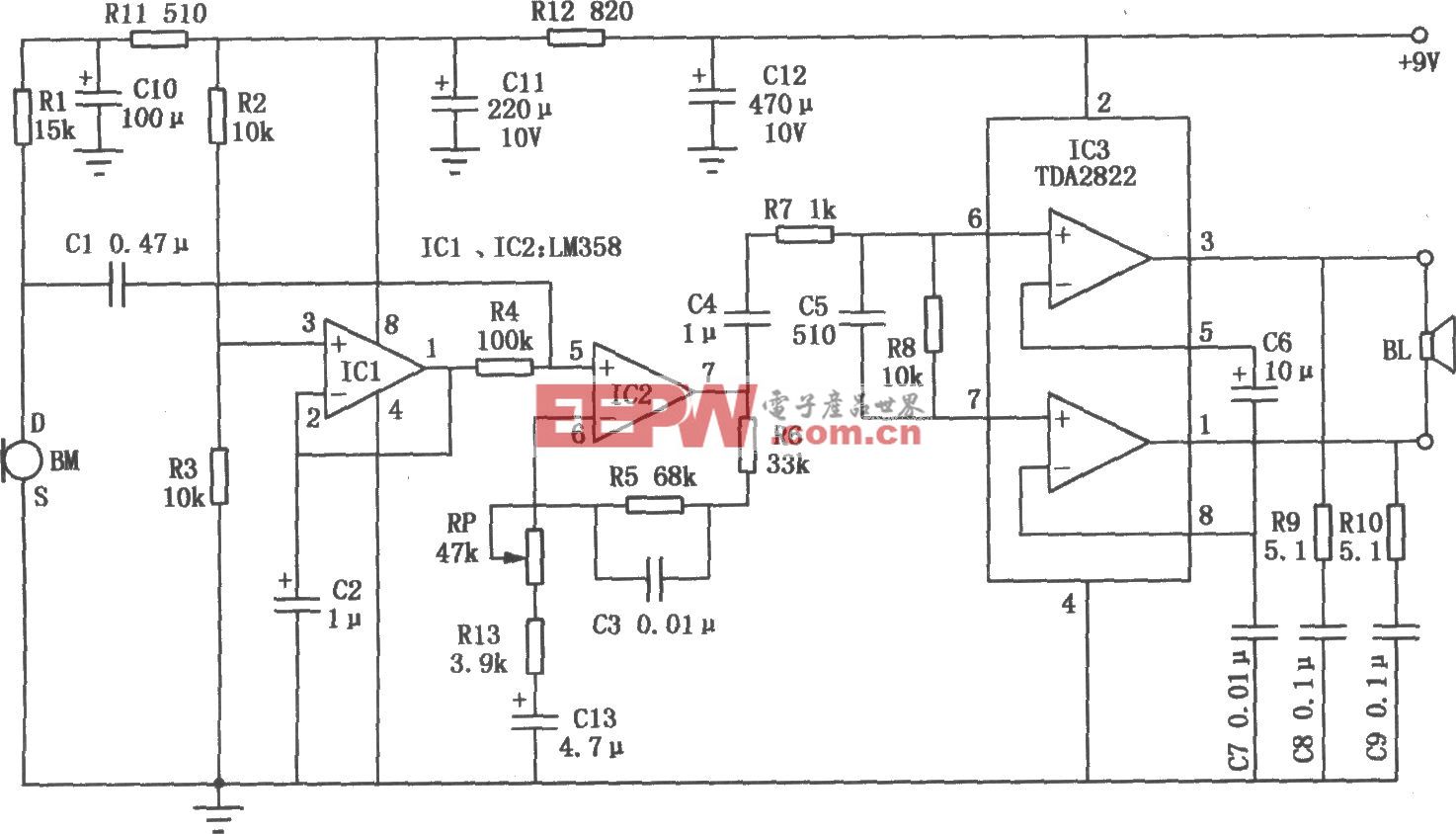

典型RFID系统由读写器(Reader)、射频标签(RFIDTag)、天线(Antenna)、中间件(Middle Ware)和应用程序(Application Ware)5部分组成。RFID系统结构框图如图1所示。读写器安装在固定位置,通过USB与PC连接,实现数据通信与读写,读写器对射频标签操作实现用户数据更新与存储。由于系统基于ISO18000-6C标准,射频标签要符合该标准,实现用户数据存储;读写器由编解码电路、数据存储电路、射频前端收发电路、天线、电源电路等构成;天线接收和发送超高频微波信号;中间件、中间信息和数据处理软件,对射频读写器和中间件事件过滤、聚合和计算,抽象出对应用软件有逻辑意义的算法;应用程序直接面对用户人机交互界面。由应用软件操作读写器,读写器收发微波信号修改用户射频标签,应用软件是用户体验和判断RFID系统成功的一个重要因素。

1.2 RFID读写器原理

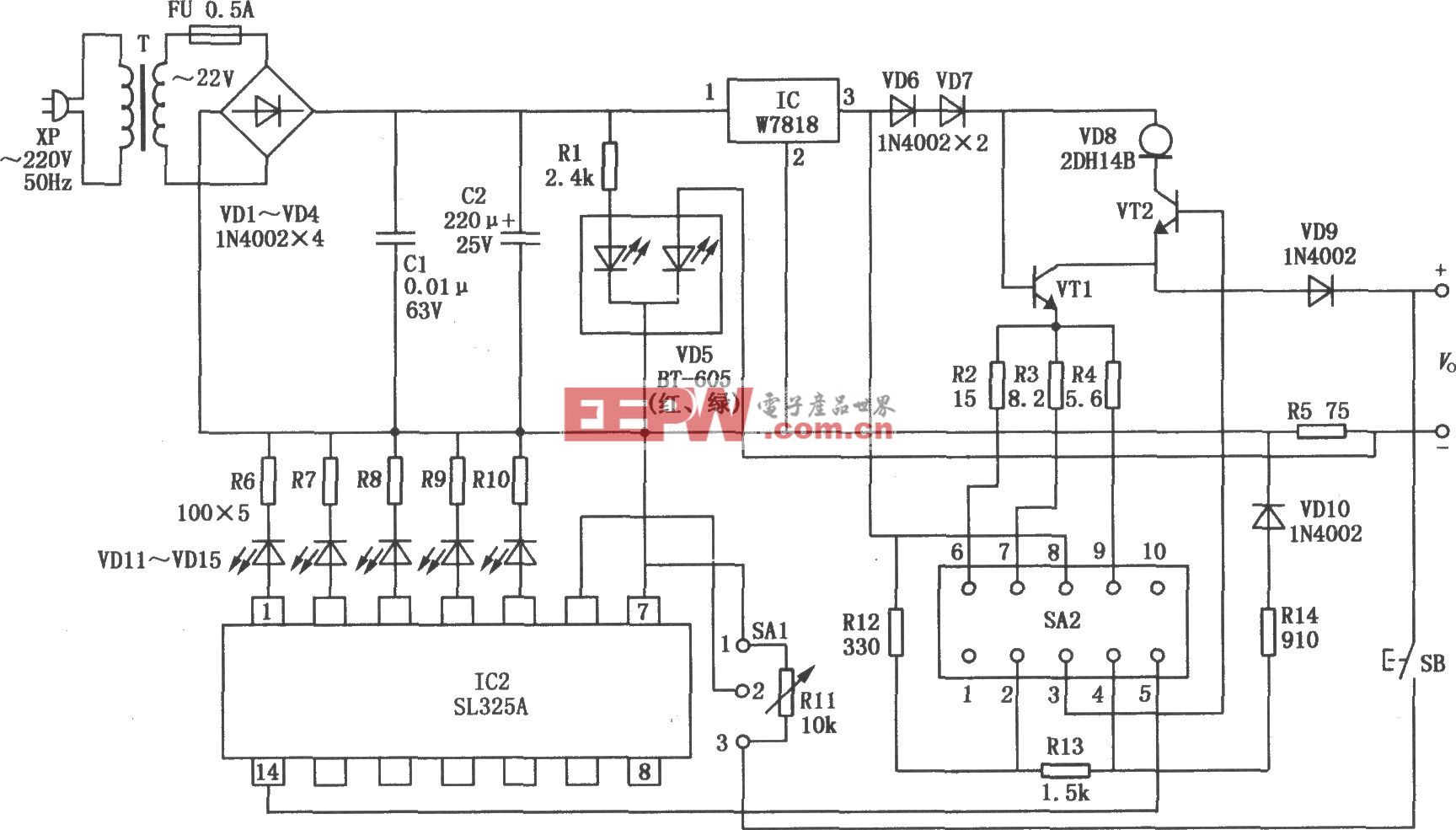

基于FPGA RFID读写器可分为3个模块:FPGA最小系统、USB串行总线接口电路、RF信号收发电路。FPGA最小系统包含FPGA现场可编程逻辑阵列、JTAG配置电路、系统时钟电路、数据存储电路、显示电路、电源电路。RFID读写器控制核心用Altera公司Cyclone系列的EP1C3T144芯片。由于FPGA基于SRAM技术,下载配置芯片用Altera公司配套的EPCS1,下载模式采用JTAG模式,20 MHz有源时钟晶振,0.3寸共阴数码管,外接5 V直流电源,经两级LM1085转换为3.3 V和1.5 V电压,为FPGA内核和引脚供电。数据存储芯片选用Catalyst公司CMOS技术芯片EEPROMCAT24WC02,通过I2C总线与FPGA连接。USB串行总线接口芯片采用南京沁恒公司的USB通用接口芯片。RF信号收发模块选用Chipcon公司的SmartRF03技术和0.18μm CMOS工艺的CC1100芯片作为微波信号收发前端,通过SPI总线与FPGA连接。

在RFID系统中,读写器是连接射频标签和PC机客户端的核心,通过对读写器命令操作,实现用户数据修改、存储等操作。RFID读写器与标签数据传输可以分为从读写器到标签前向链路和标签到读写器后向链路,前向链路与后向链路采用半双工方式通信,数据传输采用ASK调制,前向链路采用PIE码,后向链路采用Miller码,系统采用CRC-16校验码和特殊防冲突算法保证读写正确。RFID通信可分为2步:阅读器首先获得在辐射范围内标签ID号,然后对ID号符合要求的标签进行读写相应操作。读写器与上位机USB数据通信,通过USB设备枚举完成HID人机接口设备识别和数据读写。

评论