一种多通道时钟分频和触发延迟电路的设计

摘要:在EAST分布式中央定时同步系统中,时钟分频和触发延迟电路是分布式节点的核心。为了完成对基准时钟信号进行多路任意整数倍的等占空比的分频,并对输入的触发脉冲进行多路任意时间的延迟输出,本设计中采用VHDL语言进行编程,实现了多路时钟分频信号的输出和多路延迟输出,特别是提高了奇数分频和触发延迟的时间精度,最后在QuartusⅡ9.0软件上时设计的波形进行分析,验证了该设计的可行性。

关键词:EAST;时钟分频;触发延时;FPGA

0 引言

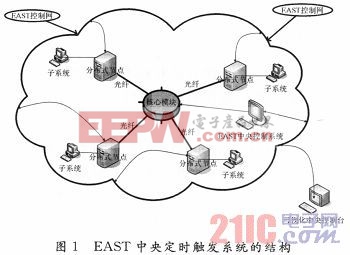

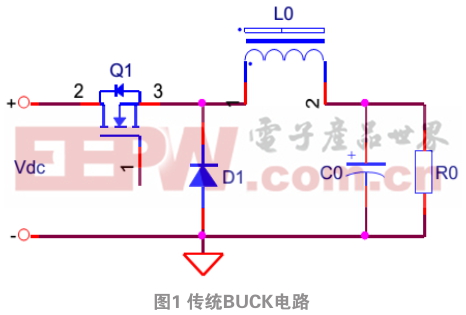

EAST(先进实验超导托卡马克)是我国自行设计研制的国际首个全超导托卡马克装置。中央定时同步系统是EAST托卡马克装置的重要组成部分。EAST中央定时与同步系统为分布广泛的数据采集系统和其它子系统提供精确的方波时钟信号,以及精确的同步触发信号,控制各子系统按照预设的时序流程工作。该系统主要由EAST可视化中央控制台,时序信号光纤网,核心模块,若干个分布式节点以及外围隔离驱动设备组成,见图1。核心模块负责向各分布式节点发送同步的基准系统时钟和系统触发信号。分布式节点根据设置对核心模块发送的基准时钟信号进行分频,得到所需要频率的时钟发送到子系统。通过设置的触发延迟模件参数可以得到子系统所需要的触发时刻。

目前,进行分频电路设计主要采用定时器来实现,8254计数器所支持的最高时钟频率有限(最高为10 MHz)以及误差较大也不是理想的实现方案。可编程逻辑器件FPGA是当今最热门的逻辑开发器件之一,它在工作最高频率、集成度、时序控制能力上具有无与伦比的优势。因此选用FPGA芯片来实现时钟分频和触发延迟电路是当前的主流。在使用FPGA做时钟分频设计时,文献设计计数器的时候用VHDL做了分频器的设计,但是只讨论了偶数的分频;文献在运动控制系统中使用Verilog描述语言在FPGA环境下对通用整数分频器进行了设计,但在通用任意整数分频器中分频系数的设置稍显复杂,不利于分布式中央定时系统,并且主要讨论的都是单路输出;文献在FPGA上实现了奇数和偶数的通用分频器,将半整数,奇数,偶数放在一个模N计数器里进行预置,这样分频系数的设定比较方便,但输出奇数分频时钟信号时的误差过大,达不到分布式定时同步系统的精度。而对触发延迟输出方面,之前这方面的研究主要采用的是模拟电路实现的方法,不易进行远程控制和更改。

本文首先介绍中央定时同步系统的基本组成结构,随后具体给出了时钟分频和触发延迟电路的逻辑设计。利用FPGA芯片来实现对输入基准时钟信号进行多通道任意整数倍的等占空比分频输出,同时对触发脉冲进行任意时刻延迟的多路输出。本设计主要采用VHDL语言来设计,利用QuartusⅡ9.0对设计进行了仿真分析,结果表明该设计满足分布式定时触发系统的分频延迟功能。

1 系统组成

EAST定时与同步系统主要由一个核心模块和多个分布式节点构成,核心模块给分布式节点提供一道基准时钟信号和一道基准触发信号,各分布式节点负责对基准时钟和触发进行分频和延时处理,为子系统系统提供它所需要的时钟和触发。总体系统结构如图1所示。

评论