基于FPGA的高精度相位差测量算法实现

摘要:首先介绍了两种高精度相位差测量算法,一种是基于直接数字频率合成(DDS)的相关测量法,另一种是基于快速傅里叶变换(FFT)的FFT测量法。其次,通过理论仿真分析两种算法在不同信噪比和数据长度下的性能,并在此基础上给出了硬件平台的设计方案。最后,基于高性能的FPGA芯片XC5SX95T,搭建了硬件实验平台,完成了两种相位差测量算法的硬件实现。经过实测,该硬件平台能够达到良好的相位差测量精度。

关键词:相位差;相关;FFT;FPGA

0 引言

两个同频信号的相位差测量在工程上有着广泛的应用。近年来,精密测量、雷达定位、目标识别等领域的高速发展对相位差测量精度和速度都提出了很高的要求。目前,理论上比较成熟的相位差测量算法主要利用相关原理和快速傅里叶变换(FFT)原理。但由于硬件环境的复杂性和不稳定性,传统硬件测量的精度往往大大低于软件计算精度,而高性能FPGA芯片的发展为硬件提高相位差测量算法的精度提供了新的方向。

本文首先介绍了两种相位差测量算法,一种是基于直接数字频率合成(DDS)的相关测量法,另一种是基于快速傅里叶变换的FFT测量法。在软件仿真的基础上,利用高性能的FPGA芯片搭建硬件实验平台,完成了两种算法的硬件实现。

1 算法原理和理论仿真

1.1 相关测量法

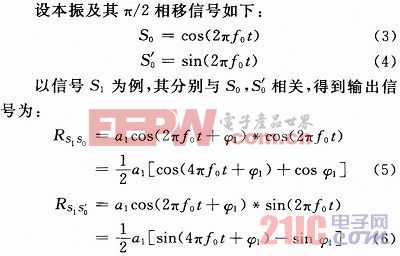

首先在接收端利用本振信号与接收信号进行相关,再经过数字低通滤波器滤除高频分量,分别得到两路接收信号的相位信息,最后相减得到相位差。由于噪声与本振信号相关性很小,所以能够很好地加以抑制。设被测信号为:

![]()

式中:f0为被测信号频率;φ1,φ2分别为两路信号的相位。两路信号的相位差△φ=φ1-φ2,即为所求。

式中,a1为相关后输出信号的幅度,由于两路本振信号的幅度一致,故相关后输出信号的幅度也可认为相等,通过低通滤波器滤除高频分量后可得:

评论