PowerPCB信号完整性整体分析设计

1.3时钟信号阻抗匹配

时钟信号是各设备工作的基础,所以时钟信号的质量尤为重要,在PCB设计时要慎重对待。

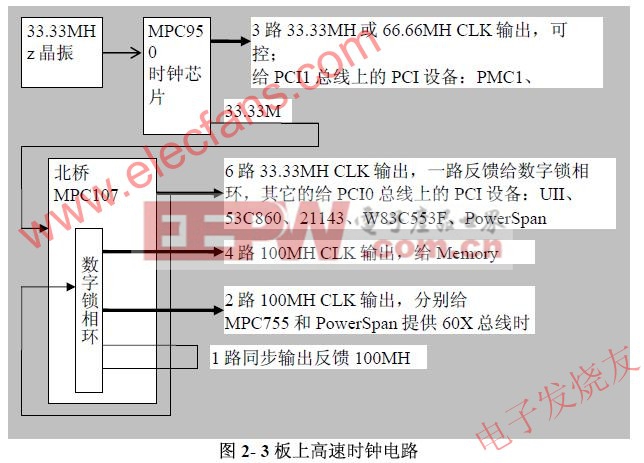

本文引用地址:http://www.eepw.com.cn/article/190762.htm板上时钟信号很多,主要高速时钟信号如图2-3所示。

时钟芯片的输出信号阻抗一般都比较小。芯片MPC950的输出阻抗为7ohm,芯片AV9155的输出阻抗为10ohm。本板上的时钟信号都是点对点连接,所以采用串行端接进行阻抗匹配电路设计。

具体串连电阻的大小由HyperLynx仿真后决定。

本板的L2Cache总线工作频率200Mhz,60x总线工作频率100MHz,是板上工作频率最高的部分。依据MPC755、MPC107、PowerSpan的芯片手册,阻抗在50ohm~70ohm之内比较合适,按前面层叠结构的设计,5mil的信号线宽是可以保证阻抗要求的。

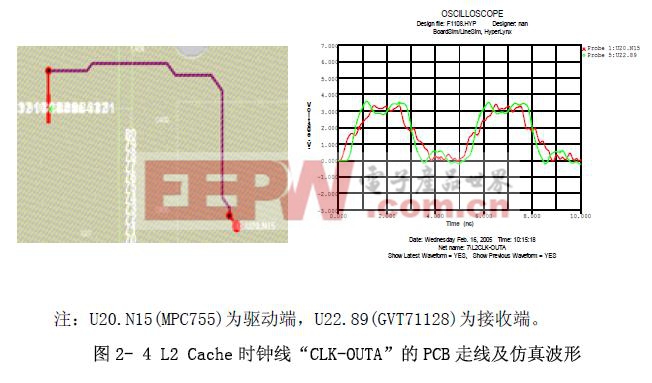

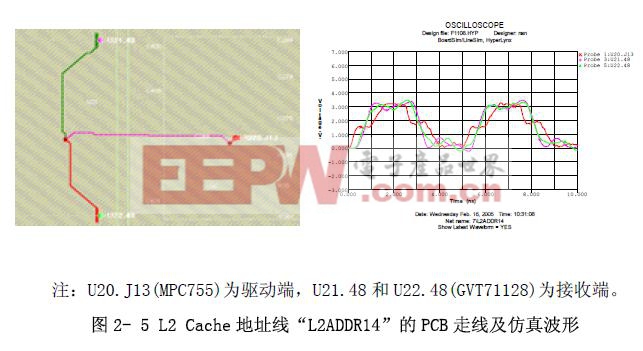

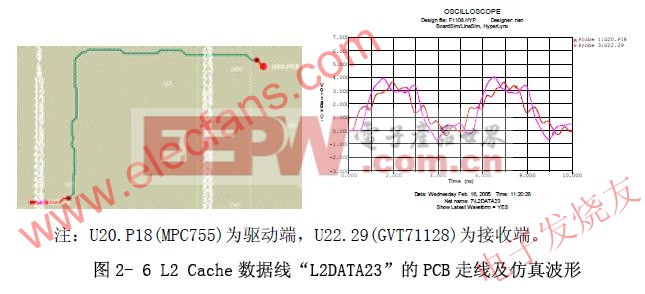

因为板上这两个总线的负载最多为2个负载,且这几个芯片之间的距离很近,相关的PCB走线很短,所以信号时序关系一般能够满足要求(尽管其工作频率很高)。下面给出L2Cache总线上典型时钟线、地址线以及数据线的PCB走线图以及在HyperLynx仿真软件的BoardSim工具下的仿真波形。MPC755、MPC107、PowerSpan和GVT71128芯片的IBIS模型均来自于芯片厂商(Motorola、TUNDRA和GALVENTECH)。

评论