利用FPGA实现与DS18B20的通信功能

FPGA需要完成DS18B20的初始化、读取DS18B20的48位ID号、启动DS18B20温度转换、读取温度转化结果。读取48位ID号和读取温度转换结果过程中,FPGA还要实现CRC校验码的计算,保证通信数据的可靠性。

以上操作反复进行,可以用状态机来实现。状态机的各种状态如下:

RESET1:对DS18B20进行第一次复位,然后进入DELAY状态,等待800μs后,进入CMD33状态。

CMD33:对DS18B20发出0×33命令,读取48位ID值。

GET_ID:从DS18B20中读取48位ID值。

RESET2:对DS18B20进行第二次复位,然后进入DELAY状态等待800μs后,进入CMDCC状态。

CMDCC:向DS18B20发出忽略ROM命令,为进入下一状态作准备。

CMD44:向DS18B20发出启动温度转换命令,然后进入DELAY状态等待900ms后进入下一状态。

RESET3:对DS18B20进行第三次复位。

CMDCC2:

向DS18B20发出忽略ROM命令,为了进入下一状态作准备。

GET_TEMP:从DS18B20中读取温度测量数值。

DELAY:等待状态。

WRITE_BIT:向DS18B20中写入数据位状态。

READ_BIT:从DS18B20中读取数据位状态。在该状态中每读取1位数据,同时完成该数据位的CRC校验计算。所有数据都读取后,还要读取8位CRC校验位。这8位校验位也经过CRC校验计算,如果通信没有错误,总的CRC校验结果应该是0。这时可将通信正确的数据保存到id和temp_data寄存器中。

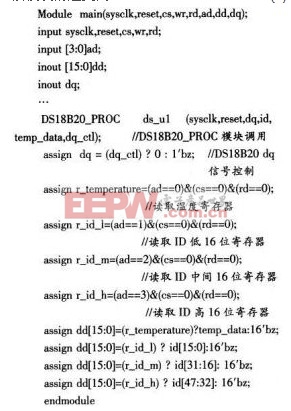

设计中采用Verilog语言建立DS18B20操作模块”DS18B20_PROC”。在该模块中实现以上的状态机功能。该模块的定义为module DS18B20?PROC(sysclk,reset,dq_pim,id,temp_data,dq_ctl)。

从仿真波形可以看出,系统上电后的10ms左右,FPGA可以读出DS18B20的48位ID值,这样,主CPU在系统复位后很短的时间内就可以读取ID值,进行相应的处理。

评论