基于NoisⅡ的程控数字信号源设计

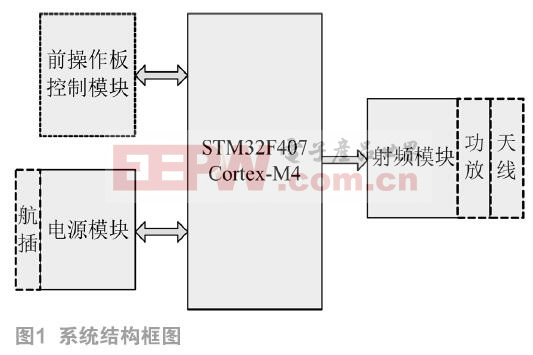

1.2 AD9854信号产生单元

AD9854的DDS核具有48位的频率分辨率。输出的信号频率最高达150 MHz、频率分辨率可达1μHz。将AD9854的8位数据线、5位地址线以及一些控制信号线(复位、寄存器数据更新引脚、FSK引脚等)引出连接到FPGA的通用I/O口上,使得FPGA可以完成对AD9854的相关配置与控制。AD9854的时钟输入采用了差分时钟输入形式。

1.3 人机交互界面

本单元由液晶显示单元和PS/2键盘输入单元组成。液晶单元采用ILI9320片上系统(SoC)驱动器。有18位数据线,采用了16 b总线宽度的i80-systemMPU接口,PWM为液晶背光亮度调节引脚;RS为寄存器选择信号,低电平选择索引或状态寄存器,高电平选择控制寄存器;

2 系统软件设计

NoisⅡ软核CPU是整个系统的控制部分,集成在FPGA内部,由SoPC Builder定制。将需要的IP组合在一起,设定各组件的地址和中断优先级,各IP Core通过Avalon总线逻辑互连,自由配置处理器的CACHE大小、指令集ROM大小、片内RAM和ROM大小、I/O引脚数目和类型、中断引脚数目、定时器数目、通用串口数目、扩展地址和数据引脚等处理器的性能指标。NoisⅡ集成开发环境提供了创建C/C++应用工程的向导、管理和编译工程功能、运行和调试程序功能和最终程序的FLASH的烧写。编程采用C语言。

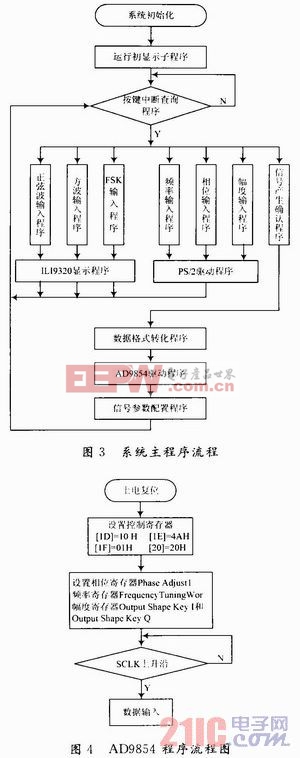

系统首先进行初始值,然后显示开机系统界面,软核CPU接收到键盘中断输入的显示信号和向AD9854输出指令后,启动显示和输出程序模块,使AD9854产生响应的信号输出。对设置数据进行存储防止设置信息掉电丢失。整体程序设计流程如图3所示。

2.1 AD9854驱动程序

(1)AD9854主要负责各种波形信号的产生,采用并行模式,其程序框图如图4所示。本文引用地址:http://www.eepw.com.cn/article/190480.htm

评论