CCD系统下基于FPGA的PCI图像采集卡设计与实现

3.2 PCI接口的设计

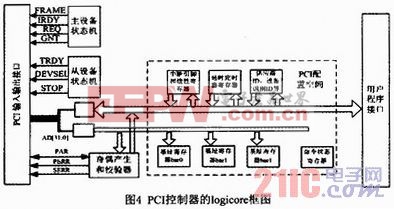

PCI图像采集卡的接口设计非常重要。由于PCI总线规范复杂,设计复杂,为了加快开发周期,采用Xilinx提供的PCI core来完成PCI总线控制器的设计。PCI控制器核logic core的内部框图如图4所示。本文引用地址:http://www.eepw.com.cn/article/190453.htm

PCI控制核主要完成用户设备和PCI总线之间的数据传输。PCI核可工作在Target传输模式和Initiator传输模式。每种传输模式又可以分单次传输和突发传输。由于单次传输速度达不到要求,我们选择突发传输模式以便提高传输速度。

Target模式下的突发传输模式相对Initiator下的突发传输模式的控制逻辑简单,但是考虑到PCI图像采集卡的可移植性,故采用Initia tor突发传输模式。在Initiator突发传输模式下,PCI图像采集卡主动向桥芯片申请PCI总线控制权,并主动传送数据;在Target模式下,必须用软件对桥芯片进行配置,也就是说PCI图像采集卡作为一个PCI从设备等待桥芯片的配置、数据读取等。所以采用Initiator下的突发传输模式逻辑控制复杂,但是移植性好。

3.3 PCI图像采集卡地址空间配置

PCI的地址空间可分为三种,分别是PCI配置空间、PCI I/O空间和PCI内存空间。

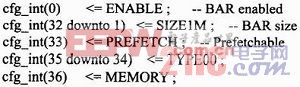

我们需要对PCI核进行配置。

Xilinx提供的PCI核提供了BAR0、BAR1、BAR2三个地址空间。这三个地址空间可以配置成内存地址空间或I/O地址空间。为了PCI图像采集卡在不同桥芯片下和不同的操作系统下工作。我们把所有的地址空间都配置成了内存空间,因为不是所有处理器都支持I/O操作。在我们的设计中,使用了BAR0和BAR1两个地址空间,配置成了内存空间,并全部配置成可以预取模式。以配制BAR0为例说明配置方法。

3.4 地址指针的设计

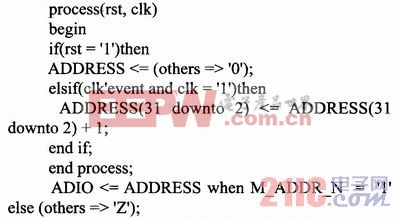

对于Initiator下的突发模式传输,因为从设备可以在任何时刻结束数据的传输,应用程序必须始终对地址进行跟踪,以便在Initiator再次发起传输时能得到正确的地址进行重新传送。

我们在设计的时候用了一个32bit的寄存器对地址进行跟踪,其中低2位始终为0,高30位用来保存数据。利用M_DATA_VLD信号来控制地址的增加。当M_ADDR_N有效的时候把地址输送到地址总线上。

3.5 Initiator突发数据传输状态机的实现

状态机用来控制突发模式的读写时序。整个状态机由六个状态组成,分别是IDLES、REOS、WRITES、READS、RSTS、OOPS。下面分对这六

个状态的功能进行描述。

IDLES:状态机处于空闲状态,状态机等待用户发起读或者写请求。

REOS:用户发起了传送请求。当是读请求时,状态机进入READS状态。当是写请求时,状态机进入WRITES状态。

READS:状态机一直处于数据读取状态直到传输完成,或者在传输过程中发生了不可恢复的错误。当数据正常传输完成时,状态机会跳到OOPS_S状态;当发生致命错误时,状态机会处于RSTS。

WRITES:状态WRITES和READS基本类似。不同的是数据传输方向不同。

RSTS:当状态机处于RSTS时说明整个系统发生了不可恢复的错误,必须重新复位让软硬件。

OOPS:当状态机处于OOPS状态,如果需要对前端的FIFO进行回滚操作,状态机就一直处于OOPS。如果前端FIFO检测传输完成信号,完成则进入IDLES状态,否则进入申请总线状态REQS。

3.6 异步存储器的实现

由于PCI读存储器的时钟频率和数据宽度与收发器写存储器的时钟频率和数据宽度不一致,所以要设计在两个异步时钟之间传输数据的接口电路。Xilinx自带的FIFO IP核是一种解决方案。但是由于异步FIFO没有Initiator突发数据传输下的需要的back_up信号,所以利用Xilinx自带的块RAM作为数据宽度可以控制的存储器。

评论