基于CPLD技术的看门狗电路设计

看门狗电路的设计

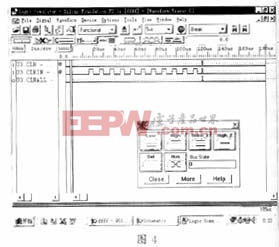

其中,CLKIN为32762Hz方波信号,CLR为分频器清零端,TIMECLK为32分频器的输出端。由该图可见,当CLR为低电平时,分频器工作,CLR为高电平时,分频器清零。

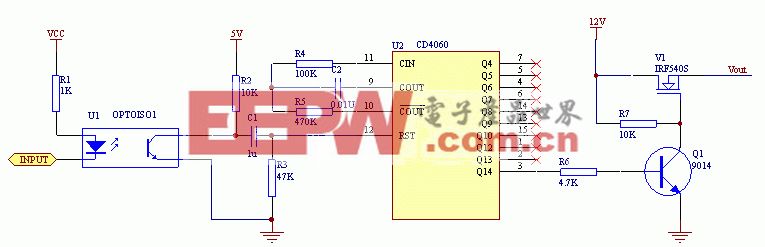

3.2 计数定时电路

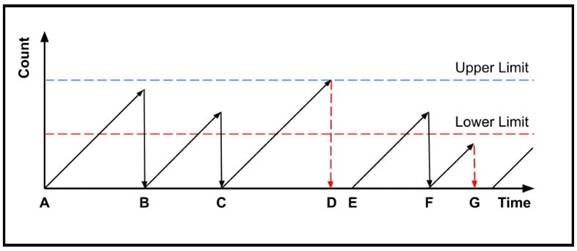

该电路是看门狗的核心电路,其功能由图1中的U5 COMP宏单元来完成,该宏单元由一个8位的二进制计数器、一个8位的寄存器和一个8位的比较器组成。其中8位寄存器的初始值为0FFH,也可通过AD BUS的8位数据口和WR DOG片选口进行置数。当1024Hz方波进入8位计数器进行计数时,比较器同时会将计数器的计数值与寄存器相比较,一旦两者相等,比较器将产生一个REST高电平,禁止计数脉冲输入同时打开复位电路中的计数器。仿真波形如图3所示。

计数定时电路本文引用地址:http://www.eepw.com.cn/article/190399.htm

其中RESTCLKIN为1024Hz基准时钟输入端。CLR为8位计数器清零端。WR为8位寄存器的片选锁存端(上升沿锁存)。DATA7为8位数据总线,用于预置8位寄存器。REST为复位输出端,提供高电平以保证系统复位。

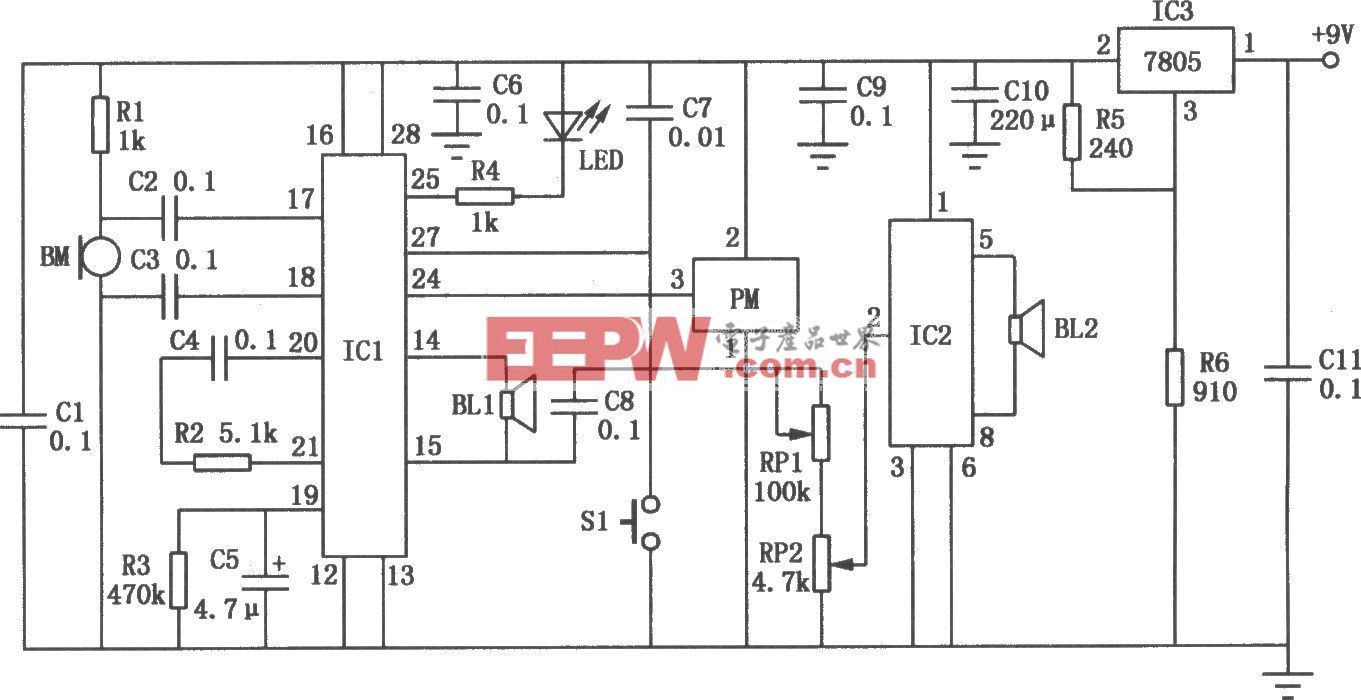

3.3 复位延时电路

该电路的功能由U3 DELAY12MS宏单元来完成,目的是在REST信号产生后,使其保持在10ms以上的稳定高电平,以保证可以实现系统可靠地复位,并在延时结束后产生一个高电平将所有宏单元计数器清零。仿真波形如图4所示。

其中,CLKIN为1024Hz基准时钟脉冲,当U5_COMP宏单元REST输出为高电平时被允许输入U3_DELAY12MS宏单元。当计数器计为12时,U3_DELAY12MS宏单元CLRALL端产生一个高电平,通过32768Hz的脉冲锁存到D型寄存器中,D型寄存器的输出端将会把所有计数器清零,使U5_COMP宏单元中比较器的输出端为“0”,从而结束复位。

4 结束语

目前,本人在所设计的产品中都采用了这种设计,实践证明,通过CPLD器件来整合看门狗电路,将能有效地保证系统正常工作,同时减小单独放置看门狗器件带来的设计风险和额外的费用。

评论