用Synplify Premier加快FPGA设计时序收敛

从 2002 年到 2003 年期间开始,很多的 EDA 供应商开始考虑将从 ASIC 中得到的具有物理意识的综合技术应用到 FPGA 设计中,但是他们并没有进一步将这种思路深入下去,而 Synplicity 公司新的基于图形的综合方法是一个例外,现在没有供应商能提供具有布局意识的 RTL 综合工具用于 FPGA 设计。问题是,与 ASIC 中的连线 “ 按序构建 ” 不同的是, FPGA 具有固定数量的预先确定的布线资源,并不是所有的布线都设置成一样 ( 某些连线短且快,某些长而快,某些短而慢,某些长而慢 ) 。

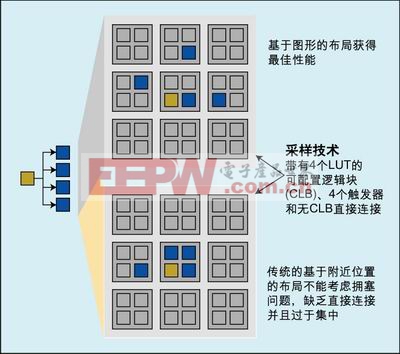

对于实际的情况而言,基于 ASIC 的具有物理意识的综合可以根据形成设计的已布局单元的附近来进行布线和时序估计。而对于 FPGA 来说,将两个逻辑功能放在相邻的区域并不一定能实现它们之间的快速连接。 - 取决于可用的布线资源,将相连接的逻辑功能布局位置更远可能反而能获得更好的布线和时序结果,尽管这有一点违背常理。这就是为什么从 ASIC 设计中得来的具有物理意识的综合技术用于 FPGA 架构时并不能得到最佳结果的原因。同样,使用这些技术的设计流程需要大量耗时的前端 ( 综合 ) 与后端 ( 布局与布线 ) 引擎之间的设计反复,以获得相关性和时序收敛。

与 FPGA 架构相关的一些考量

在详细介绍基于图形的物理综合概念之前,先了解设计任务的复杂性很重要。正如前面谈到的, FPGA 具有固定的连接资源,所有连线已经构建好,但并不是所有的路径都是一样的 ( 有短的、中等的和长的连线,而每个连线都可能具有快、中等或者慢的特性 ) 。

图 2 :比较传统和基于图形的布局。

每个路径都可能具有多个 “ 抽头点 ”( 就像高速路的出口道 ) 。这里的问题是,你可能具有一个能迅速地将一个信号从源点函数 ( 高速路的最初的入口道 ) 快速地传递到一个目的函数 ( 高速路的最后出口道 ) 的快速路径。然而,如果我们对一个内部抽头点增加第二个目的函数,这可能大大地减慢信号速度。

而且,当今 FPGA 的主流架构基于一个查找表 (LUT) 具有几个输入和单个输出的概念。一些 FPGA 架构具有通过与查找表相关的每个输入输出路径的不同延时。然而,更重要的事实是,到 LUT 的每个输入可能只能使用一部分的不同连线类型。如果来自一个 LUT 的输出驱动另外一个 LUT ,它们之间可能同时存在慢速和快速的路径,这取决于我们在接收 LUT 上所使用的特定输入 。

总的情形被 FPGA 架构的分层特性进一步复杂化。例如,一个小的逻辑模块可能有几个 LUT ;在一个较大的逻辑模块中有几个这样的小模块;在整个的 FPGA 中具有大量的这种大逻辑模块。在这些大逻辑模块中的某个逻辑块中,一个 LUT 的输出与另外一个 LUT 的输入直接相连接的概率很小;为了实现额外的连接,可能必须绕道逻辑模块的外部,然后再绕回到模块内部来实现。这一点再次地说明所处理问题的复杂性:如果你知道将它们放置在什么地方以及使用哪个引脚,将两个对象 / 实例放在不同的逻辑模块将获得比放在采用非最佳互连资源的同一模块中会得到更短的延时。

另外,任何被提出的综合方案必须解决围绕固定的硬宏资源,例如 RAM 、乘法器等相关的连线延时。同样的,方案必须解决增加的布线拥塞,这种拥塞常出现在靠近这些硬宏的地方。所有这些硬宏都属于特定器件具有的,因此任何被提出的方案必须能用于每个 FPGA 系列的每个器件。

基于图形的独特物理综合方案

能真正处理 FPGA 架构相关复杂性的具有物理意识的综合解决方案将以完全不同的观点来处理上述问题。这种方法将对 FPGA 中所有连线的特点进行描述,包括入口点、端点和内部出口点,然后对所有这些连线构建一个 “ 地图 ” 。对于软件行业来说,这种地图被称为图形 (Graph) ;这就是为什么这种方法称为 “ 基于图形的物理综合 ” 的原因。

除了连线本身,这个图形还包括这些细节:哪个 LUT 引脚连接到哪类的连线;通过每个 LUT 的输入到输出的延时差异;以及器件中的任何硬宏的大小和位置。打个比方,这类似于通过查地图来显示你将驱车经过的街道、高速路以及像停车场 ( 硬宏 ) 这样的地方。当希望穿行于城市中的两个地方时,你将使用地图来选择最快的路径,这个路径通常并不是最短的点到点路径。

类似地,基于图形的物理综合引擎不是寻找最近的路径,而是使用一种以互连为中心的方法专注于速度。从最关键的路径开始处理,然后逐步到次关键路径 ( 这样确保最关健的路径获得最快的路线 ) ,基于图形的物理综合引擎将选择连线和它们相关的入口点和出口点;从这些连线得到电路布局;从这些连线和布局得到准确的延时;最后按照要求进行优化和设计反复。

关键点是,所有的优化和反复在流程的前端部分 ( 综合 ) 执行。基于图形的物理综合的输出是一种完整布局的网表 ( 包括将与每个连线相关联的特定 LUT 引脚 ) ,这种网表可以交给 FPGA 的后端布局布线引擎。

最终得到一种一次通过的、按键操作的综合步骤,下游布局布线引擎不需要 ( 或者需要很少的 ) 设计反复。而且,根据对超过 200 个实际的设计进行分析显示,就系统的总体时钟速度而言,基于图形的物理综合可以获得 5% 到 20% 的性能提升。

本文小结

以 ASIC 为中心的具有物理意识的综合中,连线从布局选择中衍生出来,与此不同的是,在 FPGA 设计中使用基于图形的物理综合时,布局源自于连接线选择。

对于时序收敛问题,基于已有的 ( 源于 ASIC) 物理综合引擎可能需要在流程的前端 ( 综合 ) 与后端 ( 布局布线 ) 之间进行很多次耗时的设计反复。在所有这些反复之后,它们可能依然不能收敛。相比较而言,对于 200 多个采用基于图形的物理综合的设计进行分析之后显示, 90% 的设计处于最后实际时序的 10% 之内, 80% 的设计在实际时序值的 5% 以内,而采用逻辑综合的设计只有 30% 在实际时序值的 5% 以内,很多设计的误差很容易地达到 30% ,甚至更高 ) 。而且,基于图形的物理综合能提高 5% 到 20% 的总体时钟速度性能。

此外,基于图形的物理综合的已布局网表的质量大大地提高,这意味着时序驱动的布线工具的工作量很少,优化了执行,这样运行将非常快。

Synplicity 公司的突破是基于以布线为中心方法的概念,以及以图形来表示所有的东西,然后处理该图形。在经历了大量的研究和开发之后, Synplicity 的综合专家已经创建了一种真正基于图形的物理综合解决方案。第一个具有基于图表物理综合特性的产品是 Synplify Premier ,这是一种先进的 FPGA 物理综合工具,专门针对那些设计复杂、要求采用真正的物理综合解决方案的高端 FPGA 设计。 Synplify Premier 工具还包括高级的功能,例如 RTL 原级调试以及支持 ASIC 原型设计工具 Synopsys DesignWare 。本文引用地址:http://www.eepw.com.cn/article/190173.htm

评论