从StratixIII及CycloneIV开发板谈FPGA配置

如图,将拨码开关拨至PROG端,就可以用PC对EPCS64配置芯片进行烧写了。

1、先生成一个pof配置文件。在File下选择Convert Programming File,这部分操作后面也会提到。

2、将拨码开关拨至PROG,在Programmer中将模式选择为AS mode,选择pof文件。

3、Start,开始烧写。这里可以发现,过程较sof文件的烧写要漫长得多。

这里需要注意的是,其实上面图中圈起部分是很容易引起误解的。EPCS64要对FPGA进行配置时,拨码开关仍然需要拨回到RUN端,可以理解成,只是换成了配置芯片把程序烧写到FPGA中运行”罢了。

下面介绍另一种对EPCS64的配置方式,我们希望通过JTAG模式来对EPCS64进行配置。我们暂且称它为jic文件模式。这里我们可以简单把EPCS64当做一个Flash存储器,既然是存储器那肯定可以利用FPGA来对它进行写入操作。这种模式下,就是通过JTAG对FPGA进行写入操作,然后让FPGA来对配置芯片进行写入操作。

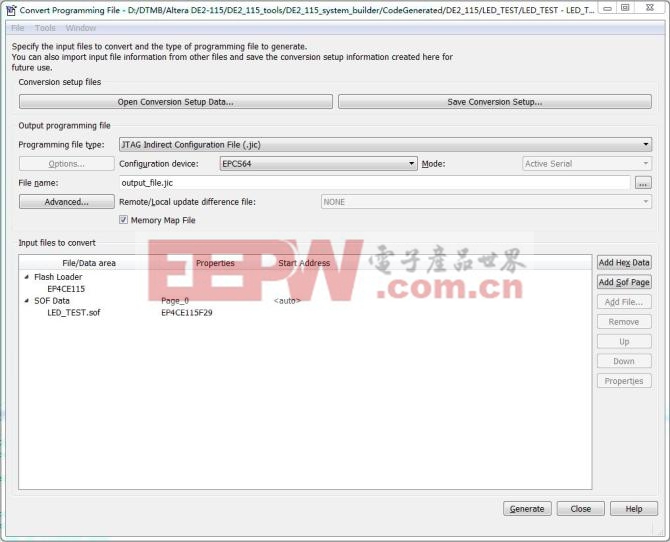

首先,还是通过Convert Programming File来生成一个jic文件。

我们可以看到在下面Input files to convert设置的时候,其中比之前的pof文件生成多了一个Flash Loader,也就是说,这里选的FPGA就是用来Loader配置芯片的。

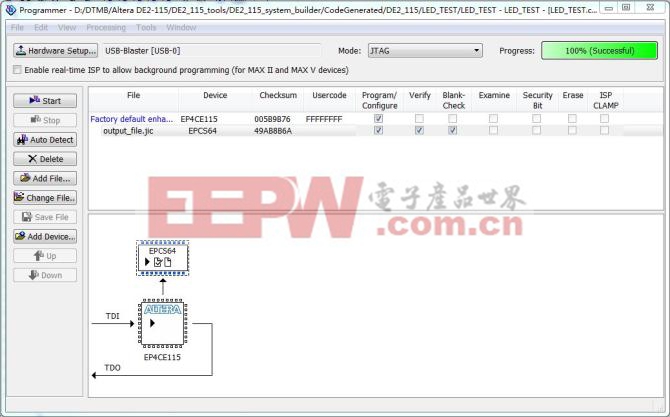

生成了jic文件后,在Programmer中选择JTAG模式下载就行了,如下图:

这里也有整个过程的体现,上图的下面也显示了整个烧写过程的简单示意图。

评论