基于CPLD的PLC背板总线协议接口芯片的设计

3.2 基于Verilog HDL 语言的硬件程序设计

本设计采用Verilog HDL 语言进行协议芯片的程序设计,Verilog HDL 语言是一种硬件描述语言,设计数字芯片时可以按照层次描述,并可以进行时序建模。本设计采用混合设计模式,主要设计的模块有状态机、协议帧检测、FIFO 控制器设计等。

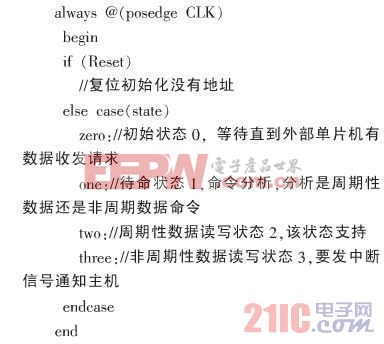

1)状态机设计。

协议芯片的顶层模块是状态控制器部分,协议芯片共有四个状态, 分别处理基于Verilog HDL 程序语言的状态机描述伪代码如下:

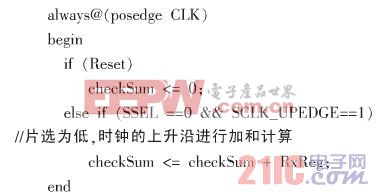

2)协议帧检测。

本协议芯片的帧校验和采用简单的加和形式进行,在接收一方,如果数据帧中有用数据的加和同后续的校验和字节相同,则协议是正确的,否则丢弃该帧。协议帧校验和计算的代码如下:

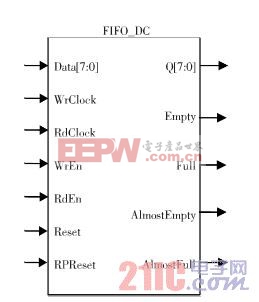

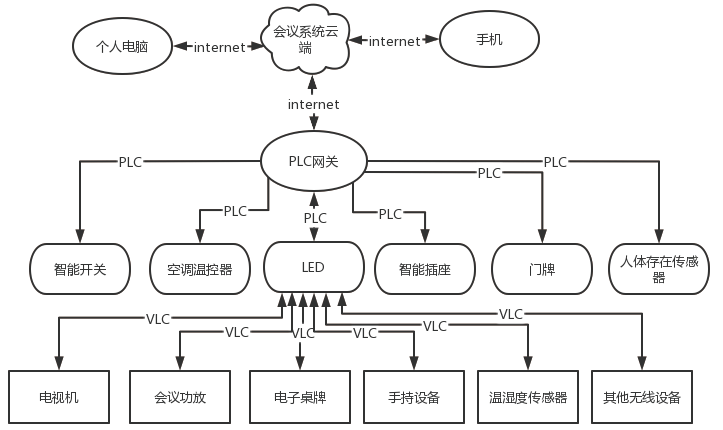

3)FIFO 设计。

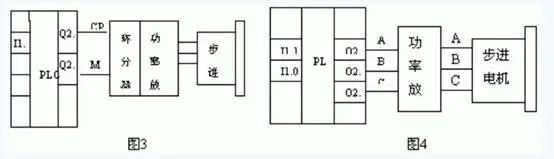

FIFO 利用了MachXO 系列CPLD 的嵌入式SRAM 块的资源,Lattice 公司的ispLEVER 7.0 软件提供了可配置的IP 软核,该软核可以采用基于嵌入式SRAM 块实现, 也可以使用查找表实现,FIFO 的IP 核框图如图4 所示,FIFO 的可配置参数包括FIFO字节深度、EmptyFull、Almostempty 和AlmostFull触发字节深度、数据宽度、大小端模式等。

图4可配置FIFO 控制器IP 软核框图

评论