基于CPLD的PLC背板总线协议接口芯片的设计

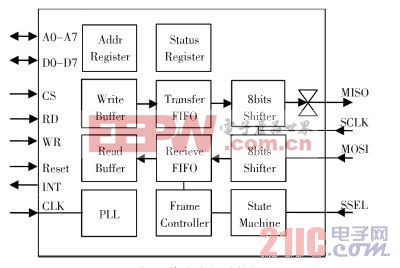

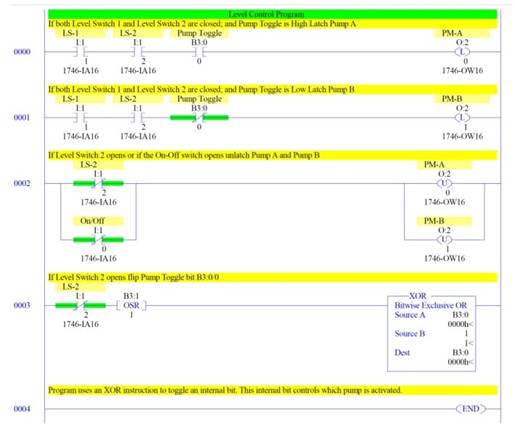

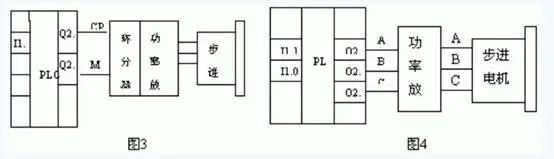

主机和从机协议芯片的内部结构框图相同,如图3 所示。

协议芯片内部有状态机控制器、帧控制器、移位寄存器、接收/发送FIFO 和读写缓存。单片机发送的周期性、非周期性数据帧,首先都写到写缓存,在发送FIFO 中进行排队发送,在SPI 时钟SCLK 的驱动下数据帧被转换为串行数据发送到背板总线;在SPI 时钟的作用下, 接收来自背板总线上的串行数据;在状态机和帧控制器的协调下,接收FIFO 中的有效数据帧被提取并放进读缓存区,等待单片机来读取,如果是非周期性数据则发中断信号通知单片机来取数据。读缓存中的周期性数据是可以覆盖的,新接收到的周期性数据直接覆盖旧的周期性数据,而非周期性数据是单独存放的,不能覆盖,由单片机读取并清除。

图3 协议芯片内部结构框图

协议芯片使得外接的单片机可以在空闲的情况下访问读缓存和写缓存,单片机不必频繁地通过中断技术处理周期性数据,也使得PLC 主机可以无等待地访问从机的周期性数据。

3 基于CPLD 的协议芯片实现

3.1 CPLD 芯片选型。

本设计选用lattice 公司的MachXO 系列芯片,该系列CPLD 集成了部分FPGA 的功能, 除了内置丰富的LUT 资源以外,还有大量分布式的SRAM 位和嵌入式的专用于FIFO 设计的SRAM 块, 并有模拟锁相环(PLL)支持时钟信号的倍频、分频等,I/O引脚可配置成1.2/1.5/1.8/3.3V 电平兼容。

评论