基于Verilog HDL语言的32X8 FIFO设计

摘要:介绍了FIFO的基本概念、设计方法和步骤,采用了一种新颖的读、写地址寄存器和双体存储器的交替读、写机制,实现了FIFO的基本功能,同时使本32X8 FIFO拥有可同时读、写的能力,完全基于Verilog HDL语言实现了电路功能并应用Synopsys公司的DesignCompiler和VCS对其进行综合、仿真。

本文引用地址:http://www.eepw.com.cn/article/189963.htm对基于单体存储器的FIFO,作为一种数据缓冲器,其数据存放结构和RAM是一致的,只是存取方式有所不同。因RAM中的各存储单元可被随机读写,故FIFO的队首位置及队列长度均可浮动。为此,需要用两个地址寄存器,分别存储读地址(即队首元素地址)和写地址(即队尾元素地址加1)。在读写过程中FIFO所存储的信息并不移动,而是通过改变读地址或写地址来指示队首队尾。

本32X8 FIFO的设计,采用了双体存储器的交替读写机制,使得在对其中一个存储器写操作的同时可以对另一个存储器进行读操作;对其中一个存储器读操作的同时可以对另一个存储器进行写操作。实现了高速数据缓冲,速度比单体存储器的FIFO提高了一倍。

1 指针以及满空信号的产生

空/满标志的产生是FIFO的核心部分。如何正确设计此部分的逻辑,直接影响到FIFO的性能。

对于同步FIFO,读写指针都指向一个内存的初始位置,每进行一次读写操作,相应的指针就递增一次,指向下一个内存位置。当指针移动到了内存的最后一个位置时,它又重新跳回初始位置。在FIFO非满或非空的情况下,这个过程将随着读写控制信号的变化一直进行下去。如果FIFO处于空的状态,下一个读动作将会导致向下溢出(underflow),一个无效的数据被读出;同样,对于一个满了的FIFO,进行写动作将会导致向上溢出(overflow),一个有用的数据被新写入的数据覆盖。这两种情况都属于误动作,因此需要设置满和空两个信号,对满信号置位表示FIFO处于满状态,对满信号复位表示FIFO非满,还有空间可以写入数据;对空信号置位表示FIFO处于空状态,对空信号复位表示FIFO非空,还有有效的数据可以读出。当读指针和写指针相等也就是指向同一个内存位置的时候,FIFO可能处于满或空两种状态。可以通过不同的方法判断或区分FIFO究竟是处于满状态还是空状态,也就是究竟是写指针从后赶上了读指针,还是读指针从后赶上了写指针。

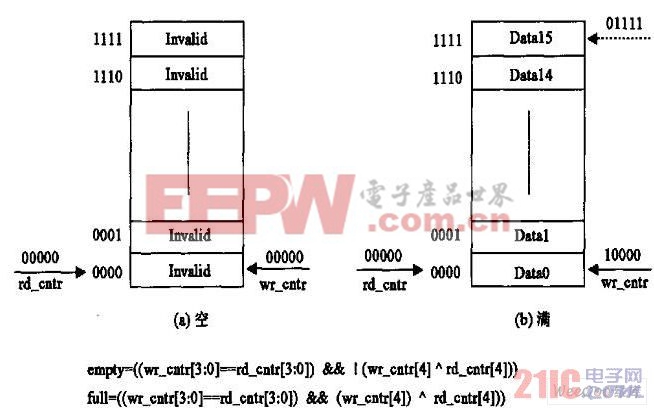

本文所应用的方法是分别将读、写地址寄存器扩展一位,将最高位设置为状态位,其余低位作为地址位,指针由地址位以及状态位组成。巧妙地应用地址位和状态位的结合实现对空、满标志位的控制。当读写指针的地址位和状态位全部吻合的时候,读写指针经历了相同次数的循环移动,也就是说,FIFO处于空状态(图1(a));如果读写指针的地址位相同而状态位相反,写指针比读指针多循环一次,标志FIFO处于满状态(图1(b))。

图1 FIFO处于的状态

评论