FCSR原理及其VHDL语言的实现

摘 要:伪随机序列发生器是序列密码设计中的重要环节,FCSR是其中一类重要思想。本文介绍了FCSR的特性和产生方法,并用VHDL语言予以实现,给出FCSR序列的主程序和仿真波形,最后指出需要注意的问题。

本文引用地址:http://www.eepw.com.cn/article/189855.htm关键词:进位移位寄存器;l-序列;VHDL;FCSR序列

伪随机信号在雷达、遥控、遥测、通信加密和无线电测量系统领域有着广泛的应用,其产生方法有多种途径。进位反馈移位寄存器(feedbackwithcarryshiftregiste,FCSR)由Klapper和Goresky于1993年提出,是一类较新颖的方法,其理论实质类似于数学上产生随机数的模2同余法。经过一系列理论分析后普遍认为在序列密码的分析和设计中具有一定价值。

本文简要介绍了FCSR的基本原理和特性,重点讨论基于硬件描述语言VHDL的可变长FCSR的设计。VHDL可编程逻辑器件CPLD/FPGA结合使用,可以方便、灵活地实现此类伪随机序列发生器。

1FCSR产生原理和序列特性

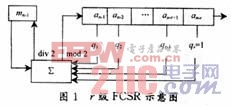

某时刻一个r级(非退化)FCSR如图1所示。其中ai∈GF(2), (i=n-1,n-2,…,n -r),mn-1∈Z,qi∈GF(2),(i=1,2,…,r-1),qr=1,∑为一般的整数加法。工作过程如下:

(1)计算整数和:

(2)移位寄存器右移一位,输出an-r。

(3) an=σn(mod 2)反馈入移位寄存器。

(4) mn=[σn/2]反馈入进位寄存器。

记q0= -1,FCSR的一个状态为(mn-1;an-1,…,

为FCSR的连接数。

FCSR能返回到自身的状态称为周期状态。以q为连接数的FCSR的周期状态个数为q+1,其中平凡的周期状态(0;0,…,0)和(w-1;1,…,1)在状态图中形成2个长为1的圈,非平凡周期状态的个数为q-1,其余状态都是非周期的。其中w=wt(q+1)为q+1的汉明重量,指qi(i=0,1,…,r)中qi≠0的个数。

以q为连接数的FCSR相应的有理数为p/q。其中,

且q为奇数。如果p和q互素,那么a有周期T=ordq(2)。特殊的,如果T=Φ(q)(φ为欧拉函数),即2为模q的本原根,那么该序列达到他的最大周期。由欧拉函数的性质可知,此时Φ(q)=q-1。称其为连接数为q的最大周期FCSR序列,或l序列。

由于在FCSR中,初始状态、移位寄存器级数、抽头数目、抽头位置的变化都会产生不同的序列,因此可以通过设计参数可变的FCSR发生器来生成周期更长的伪随机序列。

负离子发生器相关文章:负离子发生器原理

评论