快速实现SHA-1算法的硬件结构

实现结果

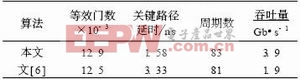

使用Verilog硬件描述语言按本文提出的优化方法实现了SHA-1算法,并使用Synopsys Design Compiler在0.18Lm标准单元库下综合,得到表1中的结果。表1中还包括了文[6]的实现结果。文[6]同样使用了0.18Lm工艺,但是实现SHA-1算法的方法仍然是传统的直接计算ABCDE5个中间变量的方法。

表1 ASIC实现结果比较

从前文的算法分析可以看出,传统实现方法的关键路径上有4次加法,如果把这4次加法按树型组织,那么关键路径的延时大约为3个32bit加法器的延时;通过本文方法改进后,关键路径延时可以缩短为1个32bit加法器延时加上少量组合逻辑延时。因此理论上速度大约可以提高为传统方法的2~3倍。从表1和使用传统方法实现的文[6]对比可以发现,实现结果和理论分析完全一致。改进方法因为计算中引入了中间变量,所以面积比传统方法要略大;同时为了计算中间变量的初值,每块数据也需要多两个周期的计算。但是因为关键路径得以明显缩短,整体的计算速度大大提高,吞吐量达到传统方法的两倍以上。

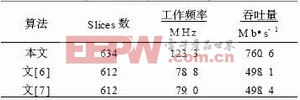

通过缩短关键路径加速SHA-1计算的方法不仅适用于ASIC设计,而且一样适用于基于FPGA的硬件设计。文[6,7]是目前常用的两种SHA-1算法的商业IP核。使用本文提出的改进方法在和文[6,7]同样的FPGA芯片上(XilinxVirtex2II系列XC2V50025)实现SHA-1算法。具体结果以及和文[6,7]结果的对比见表2。

表2 FPGA实现结果比较

结论

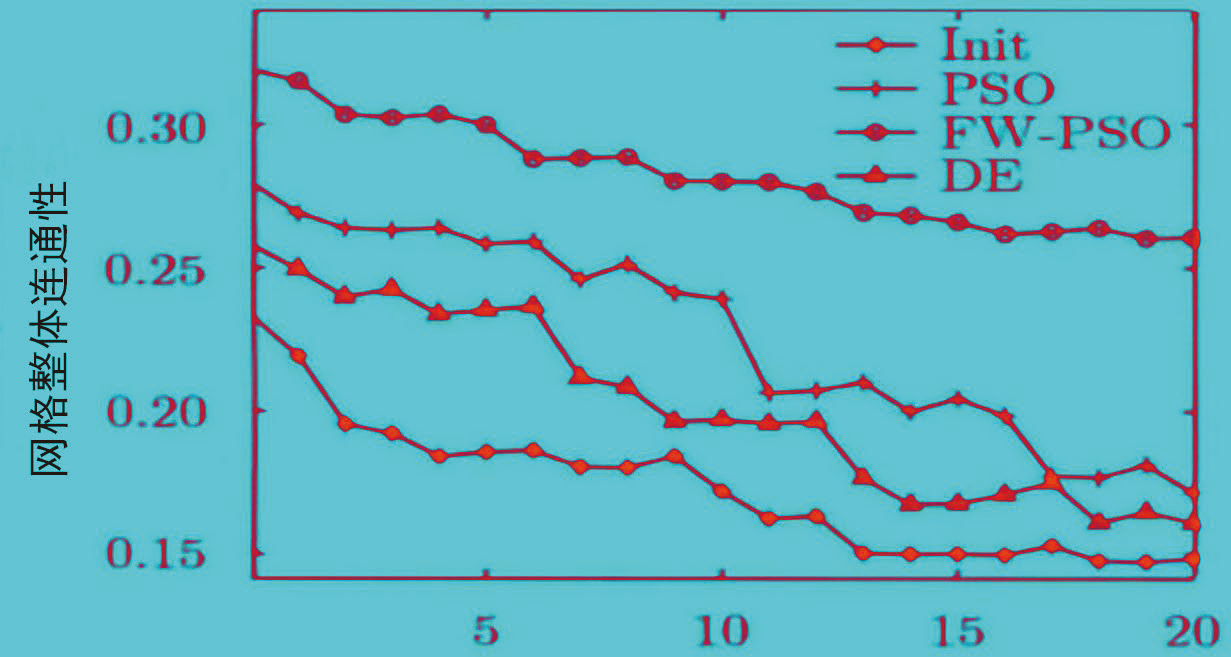

针对有理分式拟合中的保证生成二端口网络无源性的问题,本文提出了一种简单且有效的局部补偿方法,其主要思想在于:在生成网络的Y参数矩阵的对角元素上加上(相当于并联)一个RLC串联的滤波回路,使得该回路可以以恰好补偿原网络违反无源性条件的频率段,而尽量少的引入误差。经过实验表明,该方法能很好的达到预期的目的,在保证无源性条件的同时,能使引入的误差限制在2%以内。

评论