为系统设计人员提供的DRAM控制器

即使满足了这一要求,也还有其他问题。您必须对阵列预充电。预充电命令使得传感放大器中的数据无效,提升阵列和传感放大器输入之间导线上的电压,使得电压值位于逻辑0和逻辑1电平之间。这种准备是必要的,比特单元电容上很小的电荷都会传送到导线上,以某种方式提示传感放大器。

对导线进行预充电之后,您必须向新行发送一个激活命令,等待操作完成,然后,您最终可以发送一个读操作新命令。加上所有涉及到的延时后,即,读取字节序列的最差情况,每一字节都来自不同的行,这要比读取来自一个新行连续位置相同数量字节的时间慢十倍。

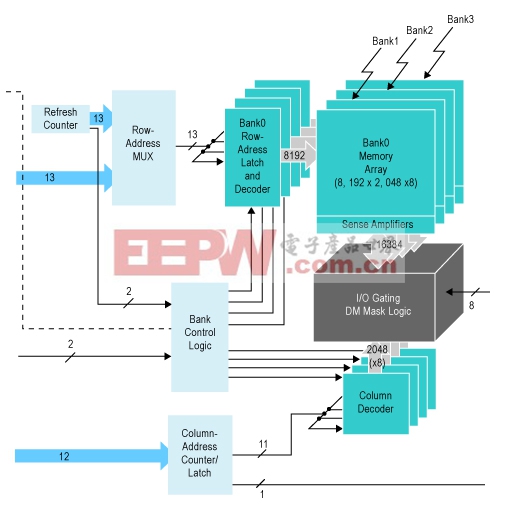

这种不同还只是部分问题。如图2 所示,DDR DRAM有多个块:与比特单元无关的阵列。DDR3 DRAM中有八个块,每一块都有自己排列成行的传感放大器。因此,原理上,您可以通过激活每一个块中的一行,读写较长的突发,然后,对每一激活后的行进行读写操作——实际上是对块进行间插操作。唯一增加的延时是连接每一块的传感放大器和芯片内部总线的缓冲的切换时间。这一延时要比对相同块中一个新行进行预充电和激活的时间短得多。

图2.一个典型的DDR DRAM结构图。一个DDR3器件会有8个块,而不是4个。

这就是原理。实际中,您可以对块进行间插处理,但是有一个限制,不是基于DRAM逻辑,而是芯片能够承受的热量。这种限制可以通过著名的“滚动四块访问窗口”,即,tRAW来表达:您一次能够有四个激活块的最长时间。这一规则实际上有例外,只要您从一个块转向下一块之前,在一个块上保持一定的时间,那么,您可以有连续激活的8个块。但是您应该知道:这比较复杂。

建立一个控制器

与前面所述不同的是DRAM时序非常复杂,接近混沌。从DRAM芯片设计人员的角度看,这非常合理,但是,很难满足多核SoC的需求。DRAM序列或者时序命令上看起来无关紧要的小改动会导致您访问存储器的带宽的巨大变化。由于存储器带宽通常是关键任务的瓶颈所在,因此,带宽的变化很快就会影响系统性能。然而,命令序列和时序来自应用程序和系统软件之间,以及系统硬件各种单元之间复杂的交互——包括缓存控制器、存储器管理器、直接存储器访问(DMA)控制器和加速器,以及DRAM控制器。

SoC的功能越来越强大,这种情况会更加复杂。目前,一个多核系统级IC会有同时运行的两个甚至更多的多线程CPU,导致共享L2高速缓存来读取指令线,随机对数据线进行读写操作。同时,计算加速器以自己的方式遍历数据结构。一个器件可以处理流视频,另一个用于矩阵乘法预读取,第三个执行路由表的随机访问。增加一个散射收集DMA控制器,处理光纤接口、硬盘和显示器之间的数据,结果是,在DRAM控制器的系统侧会有些不协调。

如果DRAM控制器只是按照系统接收顺序进行操作,那么,优化DRAM操作的工作会同等落在规划人员、设计人员和软件开发人员上——这是很难做到的。Altera公司战略市场经理Argy Krikelis提醒说:“特别是多核设计,规划人员遇到定位和性能问题。”责任落在DRAM控制器上,那么,尽可能利用其信息消除这种不协调,转换为经过优化的命令流。

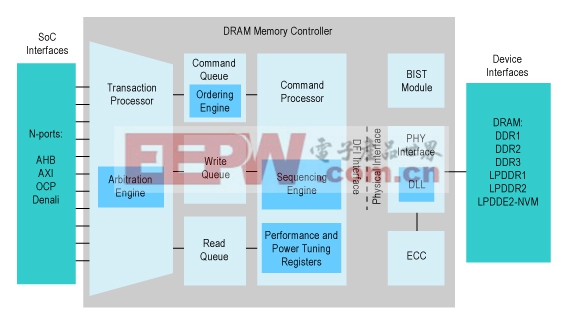

深入了解DRAM控制器就会知道,这些模块的设计人员怎样处理这些难题。您可以认为一个现代DRAM控制器有三个主要模块——物理接口、命令处理器以及事物处理器——如图3 所示。

图3.一个现代DRAM控制器涉及到事物处理器、命令处理器和物理接口。

物理接口连接DRAM芯片或者存储器模块。它读取来自命令处理器的一个命令流,将具有正确时序的命令发送至DRAM芯片,管理相关的数据字节流。接口收发器、命令和数据同步缓冲,以及产生正确命令和数据时序的状态机都含在这一模块中。而且,还有用于进行复杂的初始化操作的状态机,校准DDR3 DRAM规范设定的序列,如图1所示。此外,某些应用的物理接口还会包括自测试、诊断和误码探测以及纠错硬件。当您改变DRAM的容量或者速率等级时,必须调整物理接口。

评论