可编程逻辑器件的应用参考

控制逻辑设计

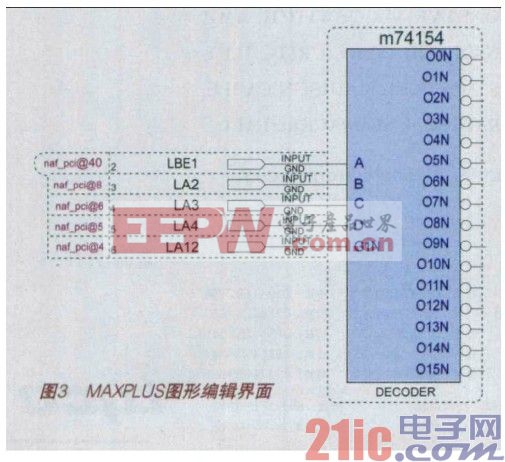

CPLD的巨大优势体现在其灵活性,可根据需要设计组合逻辑,减少了分离元件的使用,提高了系统的集成程度及可靠性。对于一般的应用采用MAX+plus编辑软件就可以完成,其界面简单,所有功能都集成于菜单中,可方便完成设计、综合、仿真、下载的全过程。图3为是应用74LS154对应软核设计的PCI接口译码电路,从而在CPLD内部实现4-16译码。电路图中可标明其用到的管脚,还可根据需要进行配置,以便于外部PCB设计的布线优化。

应用ALTERA公司的硬件开发语言AHDL及通用的VHDL等硬件描述设计语言,能实现软核的自主开发,同时可实现同步仿真,验证设计的逻辑正确性。以下是一个数字分频器设计示例。

SUBDESIGN NDivide

(

clk :INPUT;

clkoutD :OUTPUT;%偶分频输出%

BXCOUNTout[3..0] :OUTPUT;

COUNTAOUT[2..0] :OUTPUT;

)

VARIABLE

%偶分频变量%

COUNTD[3..0] :DFF;%小于16分频器,偶

数分频器%

clkRegD :DFF;

BEGIN

%偶分频部分%

COUNTD[].clk=!(clk);

clkRegD.d=!clkRegD.q;

clkoutD=clkRegD.q;

IF (COUNTD[].q==1) THEN%根据分频数定,2的n+1分

频,此处为4分频,2分频时clkRegD.clk=!clk即可%

COUNTD[].d=0;

ELSE

COUNTD[].d=COUNTD[].q+1;

END IF;

clkRegD.clk=COUNTD0.q;

END;

评论