基于FPGA的多功能频率计的设计

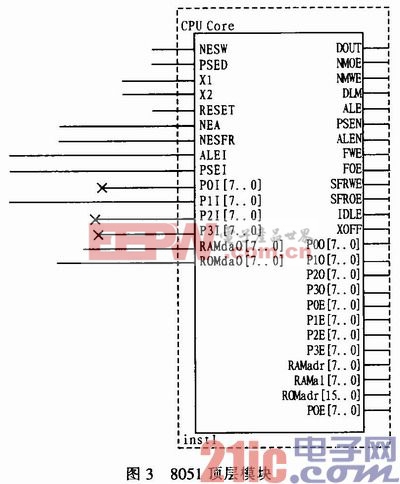

1)MC8051核。CPU_Core即MC8051单片机核如图3所示,由VQM原码表述:CPU_Core.vqm,可以直接凋用。该元件可以与其他不同语言表述的元件一同综合与编译。本文引用地址:http://www.eepw.com.cn/article/189730.htm

2)嵌入式锁相环PLL50。其输入频率设置为50 MHz,MC8051能接受的工作时钟频率上限取决于FPCA的速度级别。

3)程序ROM,LPM_ROM。采用ROM容量的大小也取决于FPGA所含的嵌入RAM的大小。设置的ROM容量是4k字节。此ROM可以加载HEX格式文件作为单片机的程序代码。HEX程序代码可以直接使用普通8051单片机程序编译器生成。

4)数据RAM,LPM_RAM。本系统设置的LPM_RAM容量是256字节。高128字节须用间接寻址方式访问。

2 等精度测频原理及FPGA设计

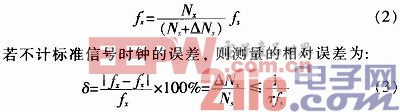

等精度测量的一个最大特点是测量的实际门控时间不是一个固定值,而是一个与被测信号有关的值,刚好是被测信号的整数倍,即与被测信号同步。这样就达到了在整个测试频段的等精度测量。等精度测频的核心思想就是通过闸门的信号与被测信号同步,将闸门时间τ控制为被测信号周期长度的整数倍。测量时,先打开预置闸门,当检测到被测信号脉冲沿到达时,标准信号时钟开始计数。预置闸门关闭时,到达时才停止,完成被测信号整数个周期的测量。测量的实际闸门时间与预置闸门时间可能不完全相同,但最大差值不超过被测信号的一个周期。设实际闸门时间为τ,被测信号周期数为Nx,标准信号频率为fs、计数值为Ns,则被测信号的频率测量值为:

![]()

由于实际闸门时间τ为被测信号周期的整数倍,因此Nx是精确的,而标准信号时钟的计数值Ns则存在误差△Ns(|△Ns|≤1),即标准信号计数的真实值应Ns+△Ns。

由此可知被测信号的频率真实值为:

可以看出,相对误差与被测信号本身的频率特性无关,即对整个测量频率域而言,测量精度相等,因而称之为“等精度测量”。标准信号的计数值Ns越大,则测量相对误差越小,即提高门限时间τ和标准信号频率fs可以提高测量精度。在精度不变的情况下,提高标准信号频率可以缩短门限时间,提高测量速度。在计数允许时间内,同时对标准信号和被测信号进行计数,再通过数学公式推导得到被测信号的频率。由于门控信号是被测信号的整数倍,就消除了对被测信号产生的±1误差,但是会产生对标准信号±1的误差。如图4所示。

系统中,采用了标准信号源的精度很高,可以达到一个很高的测量精度,本系统采用晶体作为标准信号源,因此可以达到很高的精度。

3 FPAG设计模块

本系统以Verilog HDL硬件描述语言为工具,在传统的等精度测量原理基础上进行了改进和优化。增加了测量占空比的功能,同时由FPGA内部产生清零信号,节省了资源。FPGA核心模块如图5所示。FPGA部分主要由门控信号产生模块、计数器控制模块、计数器模块、锁存器、中断输出、数据选择输出、顶层模块组成。

门控信号:时钟信号源产生频率很高的时钟信号,经过分频以后,得到频率为1 Hz、1 kHz、1 MHz和50 MHz 4种时钟信号,这些信号作为时基电路输入信测量开始,TW为1s,计数器对被测信号fsin进行计数,如果计数超过规定值9999,产生溢出信号OVERFLOW,在其作用下,量程转换电路输出信号SW状态发生变化,自动完成一次量程的换挡,同时将TW调整为0.1s,计数器重新计数。如果还有溢出信号,继续量程换挡,调整TW,直到不再有溢出信号为止。其中74160接成了一个同步四进制加法计数器,如图6所示。它的时钟输入端CLK与计数器输出端OVERFLOW(溢出)连接,在溢出信号作用下,量程转换电路输出端S1、S0依次输出00、01、10和11 4个编码,实现自动换挡。

评论